RISC architecture

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 75 → Dedup 3 → NER 3 → Enqueued 2

| RISC architecture | |

|---|---|

Konstantin Lanzet (with permission) · CC BY-SA 3.0 · source | |

| Name | RISC architecture |

RISC architecture is a class of Harvard architecture-inspired Von Neumann architecture-adjacent microprocessor design philosophies emphasizing simplified instructions and pipeline-friendly implementations. Originating from research projects at institutions such as Stanford University and the University of California, Berkeley, RISC influenced commercial products from companies like ARM Holdings, MIPS Technologies, IBM, Sun Microsystems, and Intel. The approach reshaped computing across sectors involving organizations such as Apple Inc., Microsoft, Google, Amazon (company), and Nokia.

Overview

RISC emerged alongside competing paradigms pursued by groups at Stanford University (led by John L. Hennessy) and the University of California, Berkeley (associated with David Patterson), catalyzing industry responses from DEC, Hewlett-Packard, Digital Equipment Corporation, and Motorola. Early RISC projects connected to government and academic initiatives including Defense Advanced Research Projects Agency and collaborations with laboratories like Lawrence Berkeley National Laboratory and MIT Lincoln Laboratory. The philosophy propagated through conferences such as International Symposium on Computer Architecture and journals published by IEEE and ACM, influencing standards bodies including JEDEC and ISO.

Design Principles

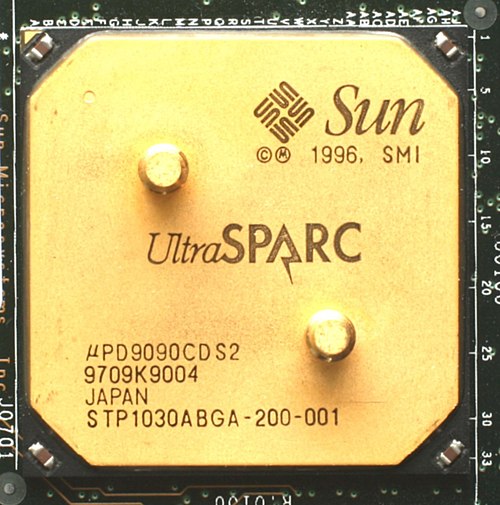

Key principles trace to research by John L. Hennessy and David Patterson, reflecting lessons from experiments at Stanford University and University of California, Berkeley. Designers prioritized a reduced set of simple, fixed-length instructions to facilitate deep pipelines and superscalar execution studied at institutions like Carnegie Mellon University and Princeton University. Architectural elements were validated by implementers at corporations such as IBM (POWER), Sun Microsystems (SPARC), and ARM Holdings (ARM), and evaluated in benchmark suites maintained by SPEC committees and organizations including Intel Corporation and AMD. Principles also intersected with compiler work from groups at University of Cambridge and ETH Zurich and microarchitectural research by teams at Bell Labs and Xerox PARC.

Instruction Set and Microarchitecture

RISC ISAs typically provide load/store semantics; this concept was explored in projects funded by National Science Foundation and implemented in chips by MIPS Technologies, ARM Holdings, and RISC-V proponents at University of California, Berkeley. Microarchitectural techniques such as register renaming, out-of-order execution, branch prediction, and pipelining were advanced by researchers at Intel Corporation, IBM, AMD, Sun Microsystems, and Hewlett-Packard. Compiler support originated in toolchains from GNU Project, Microsoft Research, and academic groups at University of Illinois Urbana–Champaign and Stanford University. Verification and formal methods from teams at CMU and MIT influenced ISA specification practices mirrored in efforts by ISO and IEEE.

Implementations and Notable RISC ISAs

Commercial and academic implementations span many actors: ARM Holdings (ARM), MIPS Technologies (MIPS), IBM (POWER/POWERPC), Sun Microsystems (SPARC), and the open initiative RISC-V championed at University of California, Berkeley with contributions from companies like SiFive and Western Digital. Other contributors include Apple Inc. (transition programs), NVIDIA (GPU control processors), Qualcomm, Broadcom, Huawei (HiSilicon), Samsung Electronics, and research groups at University of Cambridge and ETH Zurich. Microprocessor programs in governments and militaries engaged firms such as BAE Systems, Thales Group, and Lockheed Martin for embedded applications. Academic use and teaching employed simulators from PARSEC and workloads from SPEC.

Performance and Comparative Analysis

Performance comparisons involved vendors and institutions such as Intel Corporation (x86 CISC lineage), AMD, ARM Holdings, and research centers at Lawrence Livermore National Laboratory and Sandia National Laboratories. Studies published through IEEE Transactions and presented at International Symposium on Computer Architecture contrasted RISC implementations against complex instruction set models from Intel and historical designs from IBM and DEC. Metrics and benchmarking communities including SPEC, TPC, and organizations like Top500 and Green500 demonstrated trade-offs in power efficiency, throughput, and latency for deployments by Google, Amazon, Microsoft Azure, and Facebook (Meta Platforms).

Applications and Industry Impact

RISC designs powered a wide range of products and initiatives by firms including Apple Inc., Samsung Electronics, Qualcomm, NVIDIA, Cisco Systems, Ericsson, Nokia, Siemens, General Electric, and SiFive. Embedded applications in automotive, aerospace, and consumer electronics involved suppliers such as Continental AG, Bosch, Honeywell International, and Raytheon Technologies. Cloud infrastructure and data centers from Google, Microsoft, Amazon Web Services, and Facebook (Meta Platforms) explored RISC-based servers for efficiency. RISC principles influenced education and research at Stanford University, MIT, UC Berkeley, Carnegie Mellon University, and University of Cambridge, and shaped ecosystem efforts by standards organizations including IEEE, ISO, and JEDEC.