EUVL

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 84 → Dedup 0 → NER 0 → Enqueued 0

| EUVL | |

|---|---|

2pem · CC BY-SA 3.0 · source | |

| Name | Extreme Ultraviolet Lithography |

| Acronym | EUV |

| Invented | 1990s |

| Inventor | Multinational research consortia |

| Applications | Semiconductor fabrication, integrated circuits |

| Wavelength | ~13.5 nm |

| Photon source | Plasma |

| Developer | ASML, Intel, TSMC, Samsung |

EUVL

EUVL is a semiconductor photolithography technique using ~13.5 nm photons to pattern nanoscale features for integrated circuits. It evolved through multinational collaborations among ASML Holding, Intel Corporation, Taiwan Semiconductor Manufacturing Company, Samsung Electronics, IMEC, Selete, and IBM research groups. Development intersected with programs at Lawrence Livermore National Laboratory, Sandia National Laboratories, Eindhoven University of Technology, University of Tokyo, and facilities supported by European Commission initiatives.

Overview

EUVL replaces deep ultraviolet methods developed by Nikon Corporation and Canon Inc. to enable nodes pursued by TSMC and Samsung for high-density 3D NAND and FinFET scaling. Industry milestones include demonstration projects at Intel fabs, pilot production at TSMC fabs in Hsinchu Science Park, and deployment decisions by fabs owned by GlobalFoundries and captured in roadmaps from Semiconductor Industry Association and International Roadmap for Devices and Systems. The technology influenced design rules adopted by companies such as Apple Inc. and Qualcomm for mobile system-on-chip products, and affected supply chains involving Applied Materials, KLA Corporation, and Lam Research.

Technology and Operating Principles

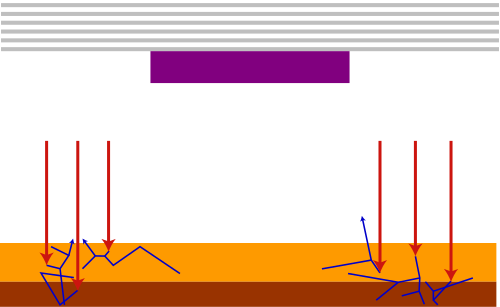

EUVL uses a ~13.5 nm photon source generated by laser-produced plasma or discharge-produced plasma in systems developed alongside lasers from Coherent Inc. and optics from Zeiss. Optical trains employ multilayer Bragg reflectors fabricated by Zeiss and ASML partners, relying on materials research from Oak Ridge National Laboratory and Max Planck Society spinouts. Masks are reflective multilayer blanks made by firms like Toppan Photomasks and patterned with electron beam tools from KLA and Thermo Fisher Scientific subsidiaries. Resist chemistry developments came from teams at DOW Chemical Company, JSR Corporation, Sumitomo Chemical, and academic groups at Massachusetts Institute of Technology, Stanford University, and University of California, Berkeley. Metrology integrates scatterometry products from KLA and inspection tools adapted by Hitachi and Nikon for pellicle and defectivity control.

Lithography Tools and Infrastructure

EUV scanners are produced primarily by ASML Holding in collaboration with subsuppliers including Zeiss, Trumpf, and Carl Zeiss SMT. Tool generations such as NXE:3100 and NXE:3400 were deployed at fabs operated by TSMC, Intel, Samsung, and SK Hynix. Cleanroom and fab infrastructure upgrades were executed at GlobalFoundries sites, Intel campuses in Ocotillo, and Samsung campuses in Hwaseong. Supply chain participants include Applied Materials for deposition, Lam Research for etch, and KLA Corporation for inspection; packaging and backend adjustments were coordinated with Amkor Technology and ASE Technology Holding. Testing collaborations involved ARM Holdings design teams and ecosystem partners such as Cadence Design Systems and Synopsys for physical verification and design rule checks.

Challenges and Limitations

EUVL deployment confronted mask defectivity challenges addressed by research at Lawrence Berkeley National Laboratory and mitigation systems developed with Toppan Photomasks and Photronics. Source power constraints and throughput issues spurred investment from ASML and laser developers like TRUMPF. Pellicle development and contamination control engaged teams from Nikon and Zeiss, while resist sensitivity and line edge roughness problems prompted collaborations with Dow Chemical, JSR Corporation, and Sumitomo Chemical. Geopolitical considerations involved export controls by United States Department of Commerce and supply agreements influenced by European Union trade policy and Dutch Ministry of Economic Affairs dialogues. Capital intensity affected fabs financed by TSMC, Intel, and Samsung, leading to joint ventures with governments of Taiwan, South Korea, and Netherlands.

Industry Adoption and Manufacturing Impact

Adoption timelines were shaped by roadmaps from Semiconductor Industry Association, tests by Intel Technology Development, and yield ramp activities at TSMC's 7 nm and 5 nm nodes used by customers such as Apple Inc. and NVIDIA Corporation. Foundry models at TSMC and GlobalFoundries integrated EUV exposure to reduce multi-patterning steps historically used by Nikon and Canon. The shift affected equipment markets where ASML emerged as a critical supplier, and procurement negotiations involved financiers such as Goldman Sachs and insurers like Marsh & McLennan. Workforce training programs were coordinated with universities including Purdue University, University of California, Santa Barbara, and Technical University of Munich to supply lithography engineers for fabs at Fab 18 style facilities.

Research and Future Developments

Research pathways include high-NA EUV systems pursued by ASML and partners, directed by roadmaps from International SEMATECH and IMEC. Advanced resist and pellicle programs involve collaborations with MIT and Caltech labs, while alternative patterning research continues at Lawrence Livermore National Laboratory and Paul Scherrer Institute. Novel light sources, fiber lasers from Coherent Inc. spin-offs, and plasma generation work at Sandia National Laboratories aim to increase source power and lifetime. Integration with next-generation transistor architectures like Gate-All-Around FETs and memory technologies such as MRAM and ReRAM is being evaluated by Samsung Advanced Institute of Technology and TSMC research groups. International coordination on standards is led by ISO committees and forums like SEMI.

Category:Semiconductor fabrication