FinFET

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 66 → Dedup 4 → NER 3 → Enqueued 1

| FinFET | |

|---|---|

Д.Ильин: vectorization · Public domain · source | |

| Name | FinFET |

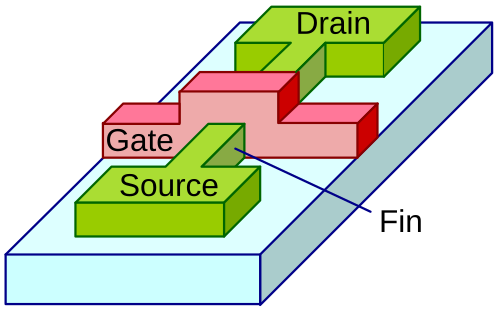

| Caption | Cross-sectional schematic of a multi-gate transistor |

| Type | Field-effect transistor |

| Invented | 1990s |

| Inventor | Chenming Hu; others |

| Developer | Intel; TSMC; GlobalFoundries; Samsung |

| Applications | Microprocessors; System-on-Chip; RF; Power management |

FinFET A FinFET is a multi-gate field-effect transistor designed to provide improved control of channel electrostatics in nanoscale semiconductor devices. The architecture emerged from academic research in the 1990s and was commercialized by major foundries and integrated circuit companies to continue scaling beyond planar metal–oxide–semiconductor field-effect transistor limits. FinFETs are central to modern microprocessor and system-on-chip production and are supported by an ecosystem of equipment manufacturers, design houses, and standards bodies.

Introduction

FinFET development involved contributions from researchers at institutions such as University of California, Berkeley, Tsinghua University, and Stanford University, and was advanced through collaborations with companies like Intel, TSMC, Samsung Electronics, GlobalFoundries, and IBM. The transition to production nodes featuring FinFETs required coordination with equipment suppliers including ASML Holding, Applied Materials, Lam Research Corporation, and KLA Corporation, and design tool integration from Cadence Design Systems, Synopsys, and Mentor Graphics. Industry consortia and standards efforts that influenced adoption include the International Technology Roadmap for Semiconductors and the Semiconductor Industry Association. Key milestones in adoption were product introductions by Intel Corporation and process node announcements from TSMC and Samsung Electronics.

Device Structure and Operation

A typical FinFET has a vertical silicon "fin" that forms the transistor channel, with the gate wrapping around one or more sides to create a double-gate or tri-gate geometry. Early conceptual work drew on electrostatic control analyses by researchers affiliated with IBM Research, Bell Labs, and Texas Instruments. The multi-gate topology reduces short-channel effects that plagued planar MOSFET scaling at the 45 nm, 32 nm, and 22 nm nodes, improving subthreshold slope and reducing drain-induced barrier lowering. Circuit designers at Intel Architecture Group, ARM Holdings, NVIDIA Corporation, Qualcomm, and Broadcom leveraged these improvements to enhance frequency, leakage power, and energy-per-operation metrics for CPUs, GPUs, and mobile SoCs. Device modeling and simulation efforts employed tools and methods from groups at NASA Ames Research Center, Sandia National Laboratories, and Argonne National Laboratory to validate electrostatic behavior and variability.

Fabrication and Materials

FinFET fabrication integrates processes from planar CMOS with additional patterning, etch, and deposition steps to form fins and wrap-around gates. Critical lithography steps involve immersion and extreme ultraviolet tools from ASML Holding; plasma etch and deposition equipment from Lam Research Corporation and Applied Materials; and metrology from KLA Corporation. Materials engineering work has explored high-k dielectrics and metal gates, with involvement from suppliers like SUMCO Corporation and Shin-Etsu Chemical. Strained silicon techniques and channel engineering used alloys and epitaxy influenced by research at Intel Labs and Samsung Advanced Institute of Technology. Process integration also drew on learnings from flash and DRAM supply chains including Micron Technology and SK Hynix, and packaging considerations from Amkor Technology and ASE Technology Holding.

Performance Advantages and Limitations

FinFETs offer advantages in threshold control, leakage reduction, and drive current versus conventional planar MOSFETs, enabling continued node scaling pursued by Intel, TSMC, and Samsung. These benefits have been quantified in technology comparisons published by industry analysts at Gartner and IC Insights, as well as in academic studies from MIT and University of Cambridge. Limitations include increased process complexity, fin-to-fin variability, parasitic capacitances, and challenges for analog and RF performance identified by teams at Qualcomm and Broadcom Wireless. Thermal management and self-heating issues have been subjects of study at IMEC and Tyndall National Institute. Cost and yield trade-offs influenced fab investment decisions evaluated by Goldman Sachs and Morgan Stanley during foundry expansion.

Variants and Design Considerations

Variants and evolutions of the FinFET concept include multi-fin FinFETs, nanosheet or nanoribbon architectures developed by Intel and TSMC, and gate-all-around proposals advanced at IBM Research and Samsung. Design considerations span fin height and width, gate length, spacer engineering, and contact formation; these parameters are optimized by process teams at GlobalFoundries and SMIC. Electronic design automation flows for FinFET-based standard cells and custom blocks were updated by Cadence Design Systems and Synopsys to support multi-patterning layout and variability-aware synthesis used by design houses like Apple Inc., AMD, ARM Ltd., and Xilinx (now part of AMD). Research into alternative channel materials and III-V integration has active programs at Purdue University, Duke University, and University of Illinois Urbana–Champaign.

Applications and Industry Adoption

FinFETs are deployed across high-performance computing, mobile, automotive, and networking markets, powering products from companies such as Intel Corporation microprocessors, Apple Inc. SoCs manufactured by TSMC, NVIDIA Corporation GPUs, and Qualcomm mobile platforms. Adoption timelines were shaped by foundry roadmaps from TSMC and Samsung Electronics and by design wins from fabless companies like MediaTek and Broadcom. The technology underpins ecosystems including cloud datacenter providers like Amazon Web Services, Google Cloud Platform, and Microsoft Azure that demand performance-per-watt improvements. Emerging applications in machine learning accelerators, automotive ADAS, and 5G infrastructure involve collaborations among NVIDIA, Intel, Qualcomm, Ericsson, and Huawei Technologies.