3D NAND

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 63 → Dedup 8 → NER 7 → Enqueued 3

| 3D NAND | |

|---|---|

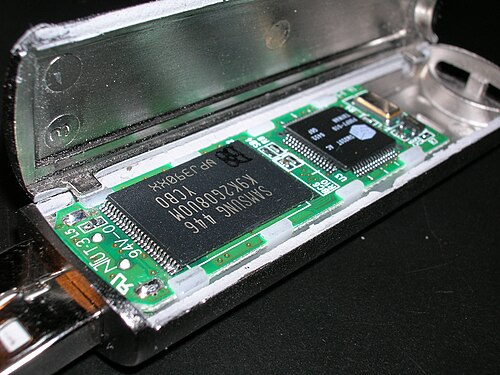

Nrbelex · CC BY-SA 3.0 · source | |

| Name | 3D NAND |

| Type | Solid-state memory |

| Developer | Toshiba, Samsung, Intel, Micron, SK Hynix |

| Introduced | 2007 (concept), 2013 (commercial) |

| Capacity | up to several terabits per die |

| Media | Floating gate / charge trap |

| Interface | NAND flash |

3D NAND 3D NAND is a multilayered non-volatile memory technology developed to increase density, performance, and cost-efficiency for solid-state storage. It evolved from two-dimensional planar NAND innovations pioneered by companies and institutions such as Toshiba Corporation, Samsung Electronics, Intel Corporation, Micron Technology, and SK Hynix and has become central to products from Western Digital Corporation, SanDisk Corporation, Kingston Technology, and server vendors such as Dell Technologies and Hewlett Packard Enterprise. The technology intersects manufacturing ecosystems of TSMC, GlobalFoundries, UMC, and equipment suppliers like ASML Holding and Applied Materials.

Introduction

3D NAND emerged as an architectural response to scaling limits encountered in planar NAND nodes promoted by standards bodies like JEDEC Solid State Technology Association and research by universities such as Massachusetts Institute of Technology and Stanford University. Early academic and industrial prototypes trace back to work at Toshiba Corporation and collaboration with research centers including IMEC and Fraunhofer Society. Commercial launches in the 2010s involved coordinated efforts across fabs operated by Samsung Electronics, Intel Corporation, Micron Technology, and joint ventures like SanDisk Corporation and Western Digital Corporation. The format is now a foundational element in consumer products from Apple Inc., Samsung Electronics mobile devices, and enterprise systems built by IBM and Oracle Corporation.

Technology and Architecture

3D NAND stacks memory cells vertically, using technologies derived from floating-gate concepts developed by firms such as Fairchild Semiconductor and academic patents from Bell Labs and University of California, Berkeley. Major architectural variants include charge trap flash (CTF) promoted by Toshiba Corporation and vertical NAND (V-NAND) branded by Samsung Electronics. Cell configurations—SLC, MLC, TLC, QLC—reflect industry trajectories similar to standards set by Intel Corporation and Micron Technology. Memory controllers from Marvell Technology Group and Phison Electronics manage wear leveling and ECC algorithms influenced by coding theory research at University of Cambridge and ETH Zurich. Interconnects and packaging integrate work from Intel Corporation on 3D stacking and from consortia like JEDEC Solid State Technology Association on form factors adopted by Samsung Electronics, Western Digital Corporation, and Kingston Technology.

Manufacturing and Scaling

Scaling 3D NAND involves lithography, etch, and deposition steps using equipment from ASML Holding, Applied Materials, and Lam Research Corporation, with process integration expertise found at TSMC and GlobalFoundries. Stacking tens to hundreds of layers required innovations similar to those in semiconductor history at Intel Corporation and process research at IMEC, while yield optimization borrowed statistical methodologies used by Texas Instruments and Analog Devices. Supply chains include chemical suppliers like DuPont and BASF SE and logistics partners such as DHL and FedEx. Economic and patent landscapes involve litigation and licensing among Toshiba Corporation, Western Digital Corporation, Micron Technology, Samsung Electronics, and SK Hynix.

Performance and Reliability

Performance metrics—read/write latency, throughput, endurance—are benchmarked by organizations like SPEC and adopted by OEMs including Apple Inc. and Dell Technologies. Error-correcting techniques and firmware strategies take cues from research groups at Cornell University and Carnegie Mellon University and commercial IP from Synopsys and Cadence Design Systems. Reliability concerns such as program/erase cycles and retention have spurred advances comparable to work at NASA for radiation-hard memories and testing regimes used by Intel Corporation in server validation. Monitoring and SMART reporting interfaces integrate standards from JEDEC Solid State Technology Association and implementation by Seagate Technology and Western Digital Corporation.

Applications and Market Impact

3D NAND underpins consumer SSDs from Samsung Electronics, Western Digital Corporation, and Crucial (brand), mobile storage in devices by Apple Inc., Samsung Electronics, and Google (company), and enterprise NVMe drives used by Amazon.com, Microsoft Corporation, and Google (company) cloud services. Data center architectures at Facebook, Inc. and Netflix rely on high-density NAND to optimize cost per bit, influencing procurement strategies at hyperscalers such as Alibaba Group and Tencent. Market dynamics affect semiconductor capital expenditure decisions at TSMC and mergers and acquisitions observed among Micron Technology and regional players regulated by authorities like the European Commission and Ministry of Commerce of the People's Republic of China.

Future Developments and Research

Ongoing research directions parallel efforts at IBM Research, Microsoft Research, Google Research, and academic labs at MIT, Stanford University, University of California, Berkeley, and ETH Zurich focusing on reliability, error correction, and novel materials from Samsung Advanced Institute of Technology and Intel Labs. Alternative non-volatile memories—ReRAM, MRAM, and PCM—pursued by Crossbar, Inc., Intel Corporation, and Everspin Technologies present complementary pathways, while 3D integration and heterogeneous packaging work with collaborators such as Intel Corporation and TSMC. Standards evolution via JEDEC Solid State Technology Association and ecosystem shifts among Samsung Electronics, Micron Technology, SK Hynix, and Western Digital Corporation will shape deployment across consumer, enterprise, and embedded markets.

Category:Computer memory