extreme ultraviolet lithography

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 51 → Dedup 7 → NER 5 → Enqueued 3

| extreme ultraviolet lithography | |

|---|---|

2pem · CC BY-SA 3.0 · source | |

| Name | Extreme ultraviolet lithography |

| Acronym | EUV |

| Introduced | 2010s |

| Developers | ASML, Intel Corporation, Samsung Electronics, TSMC, LAM Research |

| Wavelength | 13.5 nm |

| Mask | reflective multilayer mask |

| Resist | chemically amplified resist |

| Status | production |

extreme ultraviolet lithography is a photolithography technique used to pattern semiconductor devices at nanometer scale using 13.5 nm radiation. It evolved from research efforts in the European Union and the United States and is implemented by major manufacturers such as ASML, Intel Corporation, Samsung Electronics, and TSMC. EUV enabled the continuation of scaling described by Gordon Moore and influenced roadmaps set by the International Technology Roadmap for Semiconductors and the Semiconductor Industry Association.

History and development

Development traces to collaborative programs involving Lawrence Berkeley National Laboratory, Sandia National Laboratories, and the EUV LLC consortium, with key industrialization by ASML and research contributions from Tokyo Electron and Applied Materials. Early milestones include tabletop extreme ultraviolet sources developed at Lawrence Livermore National Laboratory and synchrotron experiments at the European Synchrotron Radiation Facility. Major commercialization steps involved partnerships among ASML, Carl Zeiss AG, Intel Corporation, Samsung Electronics, TSMC, and equipment suppliers such as LAM Research and KLA Corporation. Policy, export, and supplier relationships were influenced by interactions with governments including the United States, Netherlands, and China.

Principles and technology

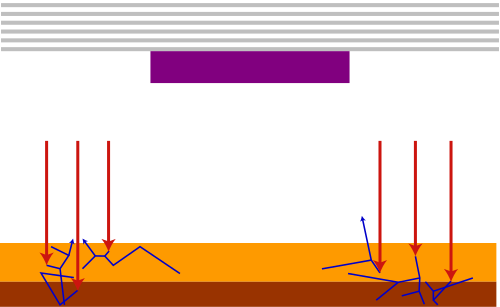

EUV operates at 13.5 nm produced by tin plasma sources developed in collaboration between ASML and suppliers; concepts stem from research at Lawrence Livermore National Laboratory and Sandia National Laboratories. EUV uses reflective optics patterned by multilayer mirrors based on Mo/Si stacks fabricated by optics specialists such as Carl Zeiss AG and characterized using metrology from KLA Corporation and Hitachi High-Tech. Masks are patterned on low-defect blanks provided by companies like GlobalFoundries partners and inspected using tools from Onto Innovation. Resist chemistry evolved through joint programs with DuPont, JSR Corporation, and Dow Chemical Company to meet sensitivity and line-edge roughness targets in collaboration with academic groups at Massachusetts Institute of Technology and Stanford University.

Equipment and components

Key systems include EUV scanners built by ASML integrating high-power sources from suppliers and collector optics from Carl Zeiss AG. Critical components include the high-power laser-pulsed tin droplet target systems developed with contributions from Axcelis Technologies partners, vacuum chambers manufactured by Edwards Group collaborators, and pellicles designed by specialists such as Nissha. Metrology and inspection rely on tools from KLA Corporation, Hitachi High-Tech, and Onto Innovation while wafer handling and process modules incorporate hardware from Tokyo Electron and Lam Research. Supply-chain coordination involved semiconductor fabs like Intel Corporation fabs, Samsung Electronics facilities, and TSMC sites to qualify tool deployment.

Applications in semiconductor manufacturing

EUV is applied to fabricate critical layers for advanced nodes used by Intel Corporation, Samsung Electronics, and TSMC for logic, memory, and advanced packaging. It enabled patterning for FinFET transistor gate layers and drove adoption for nodes marketed as 7 nm, 5 nm, and beyond as reported by the Semiconductor Industry Association and roadmaps from IEEE. EUV supports manufacturing of DRAM and NAND flash memory by companies like SK hynix and Micron Technology and is integral to designs from fabless firms such as NVIDIA, AMD, and Qualcomm where critical dimensions set performance and power characteristics specified by consortiums like JEDEC.

Technical challenges and limitations

Challenges include source power scaling pursued with partners like ASML and laser suppliers, mask defectivity requiring inspection advances from KLA Corporation, pellicle survivability developed with Nissha, and resist stochastic effects addressed by chemical suppliers such as DuPont and JSR Corporation. Optics contamination and lifetime management demanded cleanroom and vacuum engineering involving Edwards Group systems and collaborations with national labs like Argonne National Laboratory. Export controls and geopolitical considerations affected supply chains involving the United States and the Netherlands, influencing access for firms in China and prompting industrial policy responses from governments including South Korea and Taiwan.

Industry adoption and economic impact

Commercial deployment by ASML to customers Intel Corporation, Samsung Electronics, and TSMC shifted capital expenditures across the semiconductor industry, affecting tool vendors such as LAM Research, KLA Corporation, Tokyo Electron, and Applied Materials. Investment decisions by foundries and IDMs influenced M&A activity and strategic partnerships involving GlobalFoundries and fabless firms like Broadcom. The cost and throughput characteristics of EUV affected cost per transistor models evaluated by the Semiconductor Industry Association and financial analysts at firms such as Goldman Sachs and Morgan Stanley, while national strategies in Netherlands, United States, South Korea, and Taiwan adjusted incentives and industrial policy to secure advanced node capabilities.