DRAM

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 61 → Dedup 1 → NER 1 → Enqueued 1

| DRAM | |

|---|---|

| |

| Name | DRAM |

| Invented | 1960s |

| Inventor | Robert H. Dennard |

| Type | volatile memory |

| Used in | microprocessors, servers, mobile devices |

DRAM

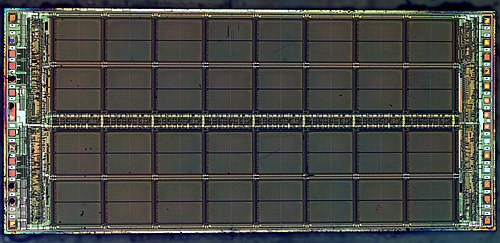

Dynamic random-access memory (DRAM) is a class of volatile semiconductor memory used as the main working storage in many computing systems. It stores each bit in a tiny capacitor and requires periodic refresh operations to retain data; this approach yields high density and moderate cost per bit, making DRAM a foundation for modern Intel Corporation-based personal computers, Advanced Micro Devices systems, and large-scale Google and Amazon data centers. DRAM development and deployment intersected with innovations from companies such as IBM, Micron Technology, Samsung Electronics, and research from institutions including Massachusetts Institute of Technology and Bell Labs.

Overview

DRAM implements bit storage using cells formed by capacitors and transistors on integrated circuits fabricated by firms like TSMC and SK Hynix; the technology contrasts with static RAM used in ARM Holdings caches and with non-volatile memories from Western Digital and Micron Technology. Key commercial standards—organized by consortia such as the JEDEC Solid State Technology Association—include generations commonly marketed by firms including Samsung Electronics, Micron Technology, and SK Hynix. The DRAM ecosystem encompasses system integrators like Dell Technologies, HP Inc., and hyperscalers including Microsoft and Facebook.

History and Development

DRAM originated from academic and industrial research in the 1960s and 1970s, building on transistor and capacitor advances pioneered at Bell Labs and industrial research at IBM Research. The seminal invention of the one-transistor one-capacitor cell is associated with researchers at Intel Corporation and with independent work by engineers linked to Texas Instruments and RCA Corporation. Commercialization accelerated with memory products from Fairchild Semiconductor, Motorola, and later by Hitachi, while standards and scaling roadmaps were influenced by roadmaps from International Technology Roadmap for Semiconductors participants and national laboratories such as Sandia National Laboratories.

Architecture and Operation

DRAM arrays are organized into banks, rows, and columns accessed via memory controllers developed by microprocessor vendors such as Intel Corporation, AMD, and NVIDIA. A typical transaction uses signals defined by interface standards promulgated by JEDEC and involves commands like ACTIVATE, READ, WRITE, PRECHARGE coordinated with controllers from firms including ARM Holdings and Broadcom. Refresh management, row hammer mitigation, and error-correcting code integration are common responsibilities of system firmware and operating systems such as Microsoft Windows, Linux (kernel), and macOS. Peripheral components and interconnects—examples include modules standardized as DIMM form factors by firms like Kingston Technology—link DRAM chips to memory buses on motherboards produced by ASUS and Gigabyte Technology.

Types and Variants

Commercial DRAM families include asynchronous and synchronous variants, with widespread products labeled SDRAM, DDR, DDR2, DDR3, DDR4, and DDR5, driven by roadmaps from companies like JEDEC and implemented by manufacturers such as Samsung Electronics and SK Hynix. Mobile variants (LPDDR) appear in devices by Apple Inc., Samsung Electronics, and Qualcomm-powered smartphones. Server-oriented variants include registered DIMMs and load-reduced DIMMs used by platforms from Intel Corporation Xeon and AMD EPYC; specialized memories such as HBM (high-bandwidth memory) partner with accelerators from NVIDIA and AI initiatives at OpenAI and DeepMind.

Performance and Scaling Challenges

Scaling DRAM faces physical and economic constraints studied at institutions like IMEC and Fraunhofer Society, including capacitor leakage, transistor variability, and dielectric reliability problems documented in research from Stanford University and University of California, Berkeley. Performance metrics—latency, bandwidth, power per bit—affect system design choices made by cloud providers such as Google and Microsoft Azure and by supercomputing centers like Argonne National Laboratory and Oak Ridge National Laboratory. Architectural vulnerabilities such as the row hammer phenomenon prompted mitigation research at universities including Cornell University and regulatory discussions with industry groups like JEDEC.

Manufacturing and Packaging

DRAM fabrication uses advanced lithography tools supplied by companies like ASML Holding and deposition systems from Applied Materials. Packaging innovations—through-silicon via and 3D stacking—are developed by foundries and packaging specialists including TSMC and Amkor Technology to produce stacked memories such as HBM adopted in accelerators by NVIDIA and supercomputers at Lawrence Livermore National Laboratory. Supply chain events affecting DRAM production have involved multinational corporations and geopolitical actors including South Korea-based firms and policymakers in Taiwan and United States trade discussions.

Applications and Future Directions

DRAM remains central to client devices from Apple Inc. and Microsoft Surface lineups, enterprise servers by Dell Technologies and HPE, and AI/ML workloads run on platforms by NVIDIA and Google DeepMind. Future directions explore alternatives and complements—such as non-volatile memories developed by Intel Corporation and research labs at IBM Research—and architectural shifts like near-memory computing pursued by teams at MIT and ETH Zurich. Industry consortia and national research programs in European Union and United States continue to fund scaling, reliability, and sustainability efforts for memory technologies.