Tensor Processing Unit

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 68 → Dedup 12 → NER 5 → Enqueued 5

| Tensor Processing Unit | |

|---|---|

Zinskauf · CC BY-SA 4.0 · source | |

| Name | Tensor Processing Unit |

| Introduced | 2016 |

| Designers | |

| Applications | Machine learning, deep learning, inferencing |

| Architecture | ASIC |

| Process | 16 nm, 7 nm (later generations) |

| Predecessor | None |

Tensor Processing Unit The Tensor Processing Unit is a family of application-specific integrated circuits created for accelerating machine learning workloads, particularly deep learning and large-scale neural network training and inference. Developed to support production services and research at Google LLC, the technology has influenced hardware strategy across the semiconductor industry, cloud providers, and research institutions like Stanford University, MIT, and Carnegie Mellon University. TPU designs span multiple generations with different trade-offs in throughput, energy efficiency, and system integration.

Overview

TPUs are proprietary ASICs optimized for numerical operations used by models such as convolutional neural networks, recurrent neural networks, and transformers. They target workloads originating from platforms like TensorFlow and are deployed in environments including Google Cloud Platform, hyperscale datacenters such as Google Data Center, and research clusters at DeepMind and university labs. The TPU program connects to initiatives like TPU Pod, Cloud TPU, and collaborations with hardware vendors and standards groups including PCI Express and Ethernet ecosystems.

Architecture

TPU architecture emphasizes large-scale matrix multiply-accumulate units, systolic arrays, and specialized memory hierarchies to accelerate mixed-precision arithmetic used in floating-point arithmetic and quantized inference. Key components mirror concepts from matrix multiplication accelerators, systolic array designs proposed in academic work at University of California, Berkeley and Massachusetts Institute of Technology. Control and host interfacing integrate with technologies like x86 and ARM server processors, while on-chip interconnects reference designs influenced by industry efforts such as Network-on-Chip research at Intel Corporation, AMD, and NVIDIA Corporation.

Hardware Implementation

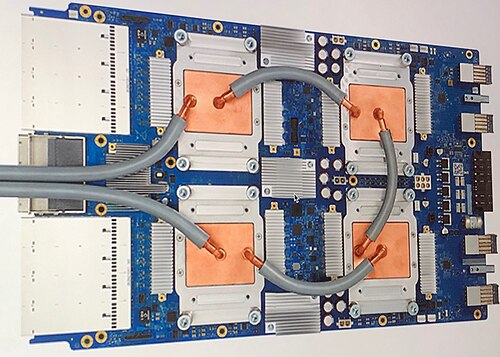

Physical implementations of TPUs have progressed across process nodes, including 16 nm and 7 nm CMOS offered by foundries like TSMC and Samsung Electronics. Packaging and cooling draw on designs from hyperscale providers such as Equinix and Microsoft Azure datacenters. TPU systems incorporate high-bandwidth memory strategies comparable to HBM2 and leverage custom power delivery and thermal solutions used by vendors like IBM in their accelerator systems. Integration with racks and pods is analogous to server designs from Dell Technologies, Hewlett Packard Enterprise, and Lenovo.

Software and Programming Model

The TPU programming model centers on TensorFlow graph compilation, XLA (Accelerated Linear Algebra), and toolchains that map high-level constructs to TPU instruction sets. Interfacing layers support APIs used by research frameworks at OpenAI, Facebook AI Research, Microsoft Research, and academic groups at University of Toronto and University of Cambridge. Compilation, profiling, and runtime tooling align with approaches from LLVM and software ecosystems like Kubernetes for cluster orchestration and Docker containerization for deployment. TPU supports mixed-precision formats influenced by standards from IEEE floating-point proposals.

Performance and Benchmarks

TPU generations report metrics for throughput (TOPS, TFLOPS), latency, and energy efficiency, often compared to accelerators from NVIDIA (e.g., Tesla V100), AMD Instinct, and Intel Ponte Vecchio. Benchmarks include training times for models such as BERT, ResNet, and large-scale transformer models used in projects at OpenAI and DeepMind. Studies from institutions like University of California, Berkeley and companies such as Facebook analyze scaling behavior across TPU Pods versus GPU clusters, examining interconnect effects similar to those in InfiniBand and Mellanox Technologies deployments.

Applications and Use Cases

TPUs power production services across Google Search, Google Photos, YouTube, and research at DeepMind for applications including language understanding, image recognition, recommendation systems, and reinforcement learning tasks. They are used for training large language models in collaborations similar to efforts at OpenAI, for scientific computing in projects at CERN, and for genomics workloads in partnerships with institutions like Broad Institute. Enterprise adoption appears in offerings from Google Cloud Platform and integrations by partners including SAP, Salesforce, and academic consortia at ETH Zurich.

History and Development

The TPU program began within Google LLC research and infrastructure teams to address bottlenecks observed in production services and research projects at Google Brain and DeepMind. Subsequent public disclosures, collaborations with cloud customers, and academic evaluations led to wider industry responses from companies like NVIDIA Corporation, Intel Corporation, and AMD. TPU evolution parallels developments in accelerator ecosystems chronicled by researchers at Stanford University, industry analyses from Gartner, and standards discussions at bodies such as IEEE.

Category:Hardware accelerators