Platform Controller Hub

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 54 → Dedup 0 → NER 0 → Enqueued 0

| Platform Controller Hub | |

|---|---|

Anas hashmi · Public domain · source | |

| Name | Platform Controller Hub |

| Introduced | 2008 |

| Designer | Intel Corporation |

| Type | Chipset |

| Markets | Personal computer, Server |

Platform Controller Hub is an Intel chipset family introduced as the successor to the PCH (Platform Controller Hub), providing input/output and peripheral connectivity for systems built around Intel microarchitectures and x86 CPUs. Designed to pair with Intel Core series processors and later Xeon CPUs, the hub unified many legacy functions into a single programmable silicon block intended to improve performance, power efficiency, and integration in notebook and desktop platforms.

Overview

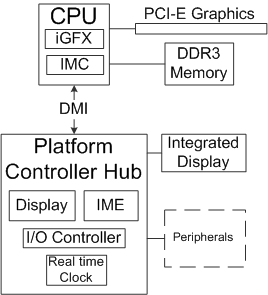

The Platform Controller Hub concept replaced the traditional two-chip chipset model used in PCs, consolidating southbound interfaces into a single device to complement Intel's direct Media Interface links on 5 Series and subsequent platforms. Productization targeted mainstream families such as 5 Series, 6 Series, and onward, aligning with processor generations from Nehalem to Skylake and beyond. Major industry partners adopting systems based on the hub include Dell, HP, Lenovo, and Apple Inc..

Architecture and Components

A typical hub integrates multiple controllers and buses: serial peripheral interfaces, USB hosts, SATA controllers, PCI Express root complexes, and audio codecs. Internally it implements fabric and bridge logic that interacts with the CPU over a proprietary link such as the Direct Media Interface used alongside Intel Core i7 and other families. Components often include an integrated Embedded Controller for power management and an integrated network interface controller for connectivity. Hardware IP blocks for RAID, AHCI, and eMMC appear in many models, while platform firmware interfaces with the hub through standards like UEFI and ACPI for system initialization and power states.

Functionality and Features

Function sets typically provide USB ports (including USB 3.0 / USB 3.1), Serial ATA (SATA) lanes supporting AHCI and RAID, PCI Express lanes for add-in cards, integrated Ethernet MACs, and integrated audio interfaces compatible with standards such as High Definition Audio. Power management features interoperate with CPU C-states and system sleep modes defined by ACPI tables authored in firmware. Telemetry and event reporting integrate with vendor management platforms like Intel Active Management Technology to enable remote diagnostics used by enterprises such as IBM and Cisco Systems.

Comparison with Southbridge/ICH

The hub concept was intended to supersede the older two-chip arrangement where the Memory Controller Hub (northbridge) and the I/O Controller Hub (southbridge) separated memory/graphics interfaces from peripheral I/O. Compared with the ICH family, the hub reduced latency by consolidating paths and by moving functions previously in the northbridge onto the CPU die, a trajectory similar to architectural shifts seen with AMD's integration of memory controllers in its Athlon 64 era. The result changed motherboard layouts and influenced OEM design practices at companies such as ASUS, MSI, and Gigabyte Technology.

Models and Chipsets

Intel released multiple series and revision families named for product lines and codes—examples include the 5 Series, 6 Series, 7 Series, and later nomenclatures used across Sandy Bridge, Ivy Bridge, Haswell, and Broadwell generations. Variants targeted form factors from ultra-low-power ultrabooks to workstation and server boards compatible with Xeon E3 and Xeon E5 product stacks. Third-party ecosystem support from BIOS vendors like AMI and firmware integrators from Phoenix Technologies shaped platform readiness across commercial devices.

Implementation and Integration

Motherboard manufacturers route the hub’s PCI Express and SATA lanes to connectors and integrated devices; OEMs map USB headers and audio codecs to front-panel connectors used by vendors such as Foxconn. Platform firmware teams implement device initialization, ACPI tables, and policy controls; operating systems including Microsoft Windows, Linux, and BSD variants ship drivers that expose hub-managed hardware such as network interfaces and storage controllers. In cloud and enterprise deployments, system integrators like HPE and Supermicro configure BIOS/firmware settings to take advantage of hub features for server management and storage configurations.

Known Issues and Security Vulnerabilities

Several platform hub families have been subject to errata, silicon bugs, and security advisories. Issues have affected USB host controllers, SATA DMA engine reliability, and PCIe enumeration under certain edge conditions documented by Intel. Security researchers and vendors such as Kaspersky Lab and Google Project Zero have highlighted either firmware-level vulnerabilities tied to management engines or side-channel exposures requiring microcode and firmware mitigations. Enterprise patching practices advised by US-CERT and vendor PSIRT teams emphasize coordinated updates across BIOS, firmware, and operating system drivers to remediate discovered flaws.

Category:Intel chipsets