Planar process

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 60 → Dedup 0 → NER 0 → Enqueued 0

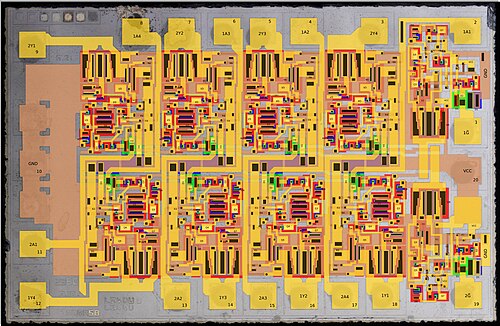

| Planar process | |

|---|---|

Robert.Baruch · CC BY-SA 4.0 · source | |

| Name | Planar process |

| Invented | 1959 |

| Inventor | Jean Hoerni |

| Developer | Fairchild Semiconductor |

| Initial use | Silicon integrated circuits |

| Key people | Jean Hoerni, Robert Noyce, Gordon Moore |

| Related | Integrated circuit, Transistor, Photolithography, Silicon dioxide |

| Country | United States |

Planar process The planar process is a semiconductor fabrication methodology developed to produce reliable integrated circuits on silicon wafers using surface passivation and photolithographic patterning. It enabled mass-manufacture of transistors and complex circuits, catalyzing growth at firms like Fairchild Semiconductor and later Intel Corporation, and it underpinned the scaling described by Moore's law. The method integrates thermal oxidation, masking, diffusion, and metallization into a reproducible sequence that transformed microelectronics, influencing projects at Bell Labs, Texas Instruments, and research at Stanford University.

History and development

The planar process emerged in the late 1950s and early 1960s through the innovation of Jean Hoerni at Fairchild Semiconductor, building on prior work at Shockley Semiconductor Laboratory and concepts from Bell Laboratories. Early demonstrations of surface passivation using silicon dioxide and the application of photolithography facilitated patterned doping and interconnects; contemporaneous figures such as Robert Noyce and Gordon Moore translated the technique into commercial integrated circuit products. The planar approach resolved reliability issues inherent in mesa and alloy processes used by companies like Texas Instruments and enabled the fabrication strategies that supported companies including National Semiconductor, Advanced Micro Devices, and Motorola Semiconductor. Subsequent decades saw incremental refinements at institutions such as Massachusetts Institute of Technology and University of California, Berkeley, and industrial alliances including SEMATECH accelerated process standardization.

Process overview

At its core the planar process relies on lateral patterning and vertical material control on a silicon substrate. Key operations combine thermal oxidation to grow a protective silicon dioxide layer, photoresist patterning via photolithography aligned with mask sets designed at facilities like Bell Labs or corporate mask shops, and dopant introduction through diffusion or ion implantation pioneered at labs such as Lawrence Berkeley National Laboratory. After doping and drive-in cycles, selective etch and metallization form interconnections; packaging and device testing at plants like Intel Fab or GlobalFoundries complete the flow. This workflow enabled repeatable device characteristics that supported mass production at fabs under management frameworks from firms such as Applied Materials and Lam Research.

Key fabrication steps

1. Wafer preparation: Starting with crystalline silicon boules produced by techniques developed at Czochralski process-oriented facilities and suppliers like Siltronic AG, wafers are sliced, polished, and cleaned in toolsets from KLA Corporation and AMAT-class vendors. 2. Oxidation: Thermal oxidation in furnaces, historically refined at Bell Labs and Fairchild, grows gate-quality silicon dioxide to protect and mask regions. 3. Lithography: Photoresist coating and exposure using mask aligners or steppers originating from companies like GCA Corporation and ASML define patterns tied to designs from organizations such as Intel Corporation and IBM. 4. Doping: Dopant introduction via liquid diffusion or ion implantation technologies developed by labs at Sandia National Laboratories and vendors including Axcelis Technologies modifies carrier concentrations for p-n junction formation. 5. Etching and cleaning: Wet and dry etch chemistries, with tools from Lam Research and Tokyo Electron, sculpt layers; wet benches and RCA cleans from methods propagated by Bell Labs assure surface purity. 6. Metallization: Deposition of aluminum, copper, or silicides using sputtering and chemical vapor deposition technologies from Applied Materials and Novellus Systems establishes interconnects. 7. Passivation and packaging: Final passivation layers and packaging integration carried out by subcontractors or in-house fabs such as Intel Fab or assemblers like Amkor Technology finalize devices.

Materials and equipment

Principal materials include crystalline silicon wafers, thermally grown silicon dioxide, photoresists supplied by chemical firms and research groups, dopant sources like boron and phosphorus, and metals including aluminum and copper. Equipment spans oxidation furnaces, mask aligners and steppers from firms such as ASML, ion implanters by Axcelis Technologies, etch tools from Lam Research, and metrology systems provided by KLA Corporation and Hitachi High-Technologies. Research institutions including Stanford University, Massachusetts Institute of Technology, and national labs contributed process recipes and characterization methods that vendors adopted for high-volume manufacturing at fabs operated by Intel Corporation and TSMC.

Variations and extensions

The planar process served as the basis for many derivatives and advancements. Complementary metal–oxide–semiconductor (CMOS) integration at Fairchild Semiconductor and Intel Corporation exploited dual-doping strategies; shallow trench isolation and CMOS scaling were pursued at IBM Research and TSMC. Ion implantation supplanted thermal diffusion in many flows, while chemical vapor deposition (CVD) and atomic layer deposition (ALD) introduced new film control, influenced by research at Bell Labs and MIT. Back-end-of-line (BEOL) copper metallization, low-k dielectrics, and multi-level interconnects emerged in collaboration with firms such as Dupont and Applied Materials, and three-dimensional integration and through-silicon via (TSV) techniques developed at Micron Technology and Imec extend planar concepts vertically.

Applications and impact on semiconductor industry

The planar process directly enabled mass production of integrated circuits used in consumer electronics, telecommunications, aerospace, and computing systems built by companies like IBM, Apple Inc., Hewlett-Packard, and Cisco Systems. It provided the process stability and yield improvements that made possible the rapid complexity growth forecast by Moore's law, fueling industries at fabs run by TSMC, GlobalFoundries, and Samsung Electronics. Standardization of planar-derived flows underpinned the fab ecosystem, supporting equipment suppliers such as Applied Materials and ASML and educational programs at Stanford University and MIT that continue to train semiconductor engineers. The planar approach remains foundational in modern CMOS technology and in research paths at institutions including IMEC and CEA-Leti.

Category:Semiconductor fabrication processes