POWER5

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 59 → Dedup 0 → NER 0 → Enqueued 0

| POWER5 | |

|---|---|

| |

| Name | POWER5 |

| Developer | International Business Machines Corporation |

| Release | 2004 |

| Architecture | POWER |

| Cores | dual-core (SMT2 per core) |

| Process | 130 nm |

| Predecessor | POWER4 |

| Successor | POWER6 |

POWER5

The POWER5 microprocessor is a high-performance server CPU developed by International Business Machines Corporation for enterprise-class systems, introduced in 2004 as part of IBM's evolution of the POWER family. It built on the lineage established by the POWER4 and influenced designs used in products from IBM System p and IBM eServer lines, impacting deployments by organizations such as NASA, Department of Energy, and commercial vendors including Sun Microsystems competitors. The design emphasized simultaneous multithreading, symmetric multiprocessing, and scalability for workloads in High Performance Computing, transaction processing, and virtualization platforms like VMware and IBM's own PowerVM.

Overview

POWER5 represented a significant step in IBM's roadmap between the POWER4 and POWER6 generations, integrating features aimed at increasing throughput for enterprise tasks used by Bank of America, Deutsche Bank, and research centers such as Lawrence Livermore National Laboratory. Introduced alongside announcements about IBM's server strategy, it targeted markets served by systems like the IBM pSeries and organizations engaged in large-scale scientific computing, including projects at CERN and academic centers at Massachusetts Institute of Technology and Stanford University.

Architecture

The POWER5 architecture extended the POWER ISA lineage with a symmetric multiprocessing design and simultaneous multithreading (SMT) capable of two threads per core, derived from research at IBM's laboratories including teams formerly associated with Thomas J. Watson Research Center. The chip continued the unified instruction and data cache strategies seen in predecessors and adopted features for coherent multiprocessing used in servers such as IBM System z cousins. Key on-chip structures reflected techniques explored in academic venues like ACM conferences and institutions including Carnegie Mellon University and University of California, Berkeley.

Performance and Features

POWER5 included enhancements for throughput and latency-sensitive operations, improving on branch prediction, out-of-order execution, and cache hierarchies to support workloads common to Oracle Corporation databases, Microsoft SQL Server implementations on ported workloads, and SAP SE enterprise resource planning systems. It added hardware support that benefited virtualization stacks such as VMware ESX and Xen-based deployments, and was used in platforms running AIX and Linux distributions from vendors like Red Hat and SUSE. Performance characteristics influenced by clock speed, pipeline depth, and SMT compared to contemporaries from Intel and AMD were reported in industry analyses by firms such as Gartner.

Implementations and Products

POWER5 served as the basis for multiple IBM server families including models in the IBM eServer p5 range and blades compatible with enterprise chassis used by HP and other datacenter integrators. It featured in configurations sold to telecom operators like Verizon Communications and content providers such as Yahoo! and eBay who required scalable I/O and memory subsystems. OEM partners and system integrators combined POWER5 chips into multi-socket systems supporting NUMA topologies used in clusters like those at Oak Ridge National Laboratory.

Software and Operating System Support

IBM positioned POWER5 to run enterprise operating systems including AIX, as well as Linux distributions maintained by Red Hat and SUSE, and middleware from IBM WebSphere and database engines from Oracle Corporation and IBM Db2. Compiler and toolchain support came from vendors and projects including GCC and proprietary IBM compilers, while virtualization and partitioning technologies such as PowerVM enabled workload consolidation for customers in finance and research who also relied on software from SAP SE and analytics platforms developed at institutions like Brookings Institution and Los Alamos National Laboratory.

Development and Manufacturing

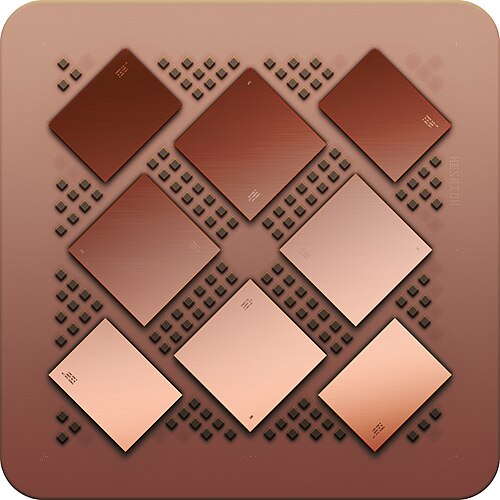

Design and microarchitecture work took place at IBM facilities including the Thomas J. Watson Research Center and development teams located near Hursley and other IBM research sites. Fabrication of POWER5 chips used foundry processes at IBM Microelectronics fabs and partner fabs; manufacturing collaborations and process engineering drew upon semiconductor industry practices shared with companies such as GlobalFoundries predecessors and discussions at industry bodies like the SEMI organization. The POWER5 family was produced on a 130 nm CMOS process with packaging and yield efforts coordinated among IBM's supply chain teams.

Reception and Legacy

The POWER5 was well-regarded in enterprise and scientific communities for its multiprocessing and SMT capabilities, influencing later designs such as the POWER6 and helping sustain IBM's presence in high-end UNIX markets confronted by competition from Oracle Corporation acquisitions and x86 vendor advances like Intel Xeon. Its impact can be traced in cloud and virtualization strategies adopted by firms including Amazon Web Services partners and legacy deployments within government labs such as Argonne National Laboratory, while academic studies at institutions like University of Cambridge examined its microarchitectural concepts. The POWER5 era contributed to debates over proprietary versus open architectures involving entities such as OpenPOWER Foundation in subsequent generations.

Category:IBM microprocessors