POWER4

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 69 → Dedup 0 → NER 0 → Enqueued 0

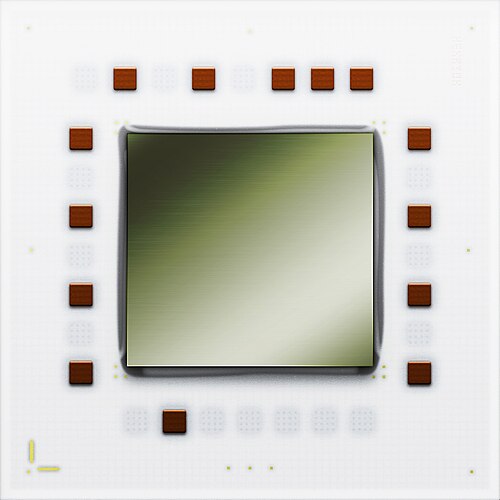

| POWER4 | |

|---|---|

| |

| Name | POWER4 |

| Designer | International Business Machines Corporation |

| Introduced | 2001 |

| Architecture | PowerPC |

| Design | Microprocessor |

| Clock speed | 1.0–1.9 GHz |

| Lithography | 0.18 µm |

| Transistors | 174 million |

| Sockets | LGA? |

POWER4

The POWER4 microprocessor was a dual-core high-performance microprocessor developed by International Business Machines Corporation for enterprise server and supercomputer markets, introduced in 2001 as part of IBM's PowerPC lineage and deployed in systems from IBM's own eServer line and collaborators such as Hitachi and Bull. It integrated two processor cores on a single die with a large shared cache hierarchy, aiming to improve throughput for database and transaction processing workloads while influencing later multicore designs used in collaborations with Motorola and Freescale Semiconductor.

History

Development of POWER4 occurred within IBM's processor groups in Austin and Poughkeepsie, New York, building on lessons from the POWER3 project and the earlier RS/6000 platform. The project aligned with strategic partnerships among IBM, Apple Inc. and Motorola in the broader PowerPC ecosystem during the late 1990s and early 2000s, while competing with microprocessors from Intel's Pentium 4 and Xeon families and Sun Microsystems' UltraSPARC line. POWER4's announcement coincided with industry shifts toward chip multiprocessing, paralleling work at organizations such as DEC (later part of Compaq), Hewlett-Packard, and research at universities like Stanford University and MIT. The processor was used in flagship IBM systems including models in the eServer pSeries and influenced alliances with vendors like Fujitsu and NEC for enterprise deployments.

Architecture

POWER4 featured a symmetric dual-core architecture with a unified on-chip second-level cache and an on-die integrated crossbar linking cores to shared resources, evolving concepts from the POWER and PowerPC 970 families. Each core implemented superscalar out-of-order execution with multiple integer and floating-point pipelines, drawing on techniques developed in academic projects at UC Berkeley and Carnegie Mellon University for branch prediction and speculative execution. The microarchitecture included simultaneous multi-threading precursors in design philosophy similar to work at Sun Microsystems on Niagara processors and shared translation lookaside buffers inspired by research at The University of Texas at Austin. Memory coherence used directory-based protocols compatible with IBM's NUMA systems found in large-scale SP clusters and earlier IBM RS/6000 symmetric multiprocessing designs. The design incorporated power, thermal and reliability strategies influenced by standards bodies like JEDEC and enterprise requirements from clients such as Bank of America and AT&T.

Fabrication and Packaging

Manufactured using a 0.18-micrometer CMOS process at IBM fabrication facilities and partner foundries including GlobalFoundries predecessors, POWER4's die housed approximately 174 million transistors and used copper interconnects and low-k dielectric techniques researched in collaboration with materials scientists at Bell Labs and IBM Research. Packaging delivered high pin-count interfaces for integration into IBM's system boards, with heat-spreading and thermal interface materials comparable to those used by Intel and AMD in contemporary server processors. The packaging enabled integration into multiprocessing backplanes in IBM chassis used by enterprise customers such as Citigroup and Siemens, meeting reliability standards highlighted by organizations such as UL and ISO.

Performance and Benchmarks

POWER4 targeted integer and floating-point throughput for enterprise workloads and HPC benchmarks, showing competitive performance on SPEC CPU2000, TPC-C, and LINPACK measurements against contemporaries from Intel and Sun Microsystems. The dual-core die with large on-chip cache provided improved cache coherence and reduced memory latency for OLTP tasks used by Oracle Corporation and Microsoft SQL Server installations on IBM hardware. Compiler support from vendors such as GNU's toolchain and proprietary compilers from IBM and Habanero Systems (research groups) enabled optimizations exploiting wide superscalar pipelines; performance tuning guides were distributed to partners including SAP and Oracle. POWER4's instruction throughput influenced later benchmark methodologies used by organizations like SPEC and research groups at Lawrence Livermore National Laboratory.

System Implementations

POWER4 was integrated into IBM's midrange and high-end servers including models in the eServer pSeries and high-performance computing racks used in clusters at national labs such as Los Alamos National Laboratory and Argonne National Laboratory. Systems from OEM partners like Hitachi and Bull used POWER4-based boards for transaction processing centers at companies including JPMorgan Chase and telecommunications carriers such as Verizon. The processor appeared in blade and rack configurations compatible with enterprise virtualization solutions from companies like VMware and middleware stacks from IBM WebSphere and Oracle WebLogic.

Variants and Successors

POWER4 led to derivatives and influenced subsequent IBM processors including follow-on designs in the POWER5 family and the scalable multicore roadmap that encompassed processors used in the Blue Gene project and later POWER9 developments. The architectural lessons from POWER4 informed collaborations with Motorola and later Freescale Semiconductor's multicore approaches, and inspired academic and commercial designs in multicore research at institutions like University of Illinois Urbana-Champaign and companies such as AMD exploring chiplet and multicore scaling. Successor processors improved simultaneous multithreading, cache hierarchies, and interconnect fabrics used across IBM's enterprise and HPC product lines.

Category:IBM microprocessors Category:PowerPC microprocessors