PN junction

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 79 → Dedup 0 → NER 0 → Enqueued 0

| PN junction | |

|---|---|

Raffamaiden · CC BY-SA 3.0 · source | |

| Name | PN junction |

| Type | Diode junction |

| Invented | 1940s |

| Inventor | Russell Ohl, William Shockley, John Bardeen, Walter Brattain |

| Applications | Transistor, Photovoltaic cell, Light-emitting diode, Rectifier |

PN junction

A PN junction is a fundamental semiconductor interface formed between regions doped with acceptors and donors, serving as the core building block of many solid-state devices. It underpins the operation of diodes, transistors, photovoltaic cells, and optoelectronic components, and its study connects semiconductor physics, materials science, and electronic engineering. Key historical figures and institutions advanced its theory and application during the mid‑20th century, linking laboratories at Bell Labs, research at Massachusetts Institute of Technology, and developments in the electronics industry around Silicon Valley.

Introduction

The PN junction emerged from experiments and theory developed by researchers such as Russell Ohl, William Shockley, John Bardeen, and Walter Brattain at places like Bell Laboratories and academic centers including Stanford University and University of Illinois Urbana–Champaign. Its behavior is described by pioneers of semiconductor theory connected to works by Albert Einstein (photoelectric investigations), Arthur Schawlow (optical transitions), and later advances from researchers at Bell Labs that led to the transistor revolution recognized by awards such as the Nobel Prize in Physics. The device links to commercial and military applications in companies like Fairchild Semiconductor and Texas Instruments and influenced standards set by organizations such as IEEE.

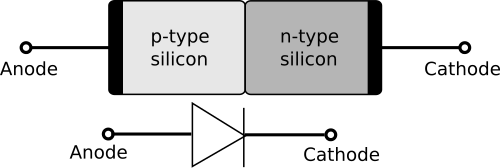

Structure and Formation

A PN junction forms in crystalline materials like Silicon and Germanium when regions are doped with acceptor impurities (e.g., Boron) and donor impurities (e.g., Phosphorus), using techniques developed in facilities such as Semiconductor Manufacturing International Corporation and research fabs at IBM Research. The interface exhibits a depletion region whose width depends on doping profiles controlled by processes from equipment vendors like Applied Materials and ASML. Formation methods trace to diffusion and ion implantation processes refined in laboratories at institutions like Bell Labs and industrial sites including Intel fabs. Crystallographic orientation of substrates provided by suppliers such as Siltronic influences defect populations studied by groups at Lawrence Berkeley National Laboratory and Argonne National Laboratory.

Electrical Characteristics and Theory

The junction’s electrical behavior follows principles from carrier statistics and transport formalized by theorists associated with Cambridge University and University of California, Berkeley. Under forward bias it exhibits exponential current–voltage relation described by the Shockley diode equation, while reverse bias leads to breakdown phenomena analyzed by researchers at Sandia National Laboratories and Los Alamos National Laboratory. Carrier recombination, generation, diffusion lengths, and lifetimes were characterized in experiments at Bell Labs and modeled using formalisms developed by figures connected to Nobel Prize recognition. The junction’s capacitance, described in terms of depletion charge, is key to switching performance in circuits used by companies like AMD and Nvidia and in standards from JEDEC.

Fabrication Methods

Manufacturing of PN junctions employs thermal diffusion, ion implantation, epitaxial growth, and molecular beam epitaxy techniques refined by teams at MIT Lincoln Laboratory and corporate research centers like Intel Labs. Photolithography steps, derived from advances in optics by researchers at Nikon and ASML, define junction geometries; annealing is performed with systems from Applied Materials and Tokyo Electron. Contamination control is practiced in cleanrooms following protocols from SEMI and standards used in fabs at TSMC and GlobalFoundries. Characterization tools such as scanning electron microscopes from FEI Company and Hall effect systems developed at Oxford Instruments are routine in process control.

Applications and Devices

PN junctions enable diodes, bipolar junction transistors, junction field‑effect transistors, solar cells, LEDs, photodiodes, and detectors used by industries and research centers including RCA, General Electric, Siemens, and national labs. Photovoltaic modules deploying junctions are central to projects funded by agencies like NASA and DOE; LEDs employing heterojunctions were commercialized by companies such as Cree and Osram. Integrated circuits realized by firms like Intel and AMD incorporate billions of PN junctions; sensors in experimental apparatus at CERN use specialized junction devices. The junction’s role in power electronics is central to products from Infineon Technologies and STMicroelectronics.

Performance Limitations and Nonideal Effects

Real devices show series resistance, leakage currents, breakdown mechanisms (Zener and avalanche), and noise contributions analyzed by researchers at Bell Labs and Texas Instruments. Surface states, interface traps, and recombination centers tied to processing at foundries like TSMC and contamination incidents investigated by NIST degrade ideal behavior. High‑frequency limits and thermal runaway are key concerns in power modules designed by ABB and Schneider Electric and in aerospace applications supported by Lockheed Martin research. Reliability challenges are studied in programs at Sandia National Laboratories and by consortia such as SEMI.

Advanced Variants and Modern Developments

Heterojunctions combining materials like Gallium Arsenide, Indium Phosphide, and Gallium Nitride enable high‑speed and optoelectronic devices developed at IMEC and by firms like Skyworks Solutions and Broadcom. Novel junction concepts such as tunnel junctions, superjunctions, and graded‑bandgap structures are advanced in academic groups at University of Cambridge and industrial labs at Nokia Bell Labs. Research into two‑dimensional materials (e.g., Graphene, Transition metal dichalcogenides) and integration with silicon photonics pursued at IBM Research and Corning Incorporated promises new device paradigms. Funding and coordination for these efforts come from agencies such as European Research Council, National Science Foundation, and national innovation programs in China and Japan.