Fast Page Mode DRAM

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 53 → Dedup 0 → NER 0 → Enqueued 0

| Fast Page Mode DRAM | |

|---|---|

| |

| Name | Fast Page Mode DRAM |

| Type | Dynamic random-access memory |

| Invented | 1970s |

| Developer | Multiple semiconductor manufacturers |

| Predecessor | Static RAM |

| Successor | Extended Data Out DRAM, Synchronous DRAM |

Fast Page Mode DRAM

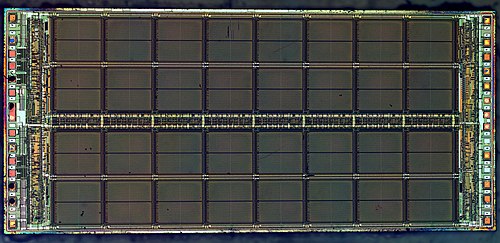

Fast Page Mode DRAM is an early dynamic random-access memory variant optimized for repeated accesses within a single memory row, enabling higher throughput for bursty workloads. Originating in the late 1970s and standardized through industry practice rather than a single patent, it served as a bridge between single-access DRAM chips and later burst-oriented designs like Extended Data Out DRAM and Synchronous DRAM. Fast Page Mode DRAM found broad adoption in personal computers, workstations, and embedded controllers during the 1980s and early 1990s.

Overview

Fast Page Mode DRAM was implemented by multiple semiconductor firms to exploit locality within a single opened memory page. Semiconductor companies including Intel Corporation, Micron Technology, Texas Instruments, NEC Corporation, Hitachi, and Motorola produced compatible devices for industry platforms such as the IBM PC/AT and early Apple II successors. The architecture emphasized reduced latency for successive column accesses after a row has been activated, making it attractive for microprocessor designs from Intel 8086 onwards and for chipset vendors like VIA Technologies and AMD. Its adoption dovetailed with motherboard standards such as the AT form factor and with bus controllers developed by firms like National Semiconductor.

Architecture and Operation

Fast Page Mode DRAM retains the fundamental cell array and sense-amplifier organization common to dynamic memories used by manufacturers like Samsung Electronics and Toshiba Corporation. A typical device exposes address lines, data I/O pins, and control signals compatible with memory controllers from Cirrus Logic or SiS (Silicon Integrated Systems). Operation relies on opening a row (activating a wordline) to transfer a full page into sense amplifiers, then performing multiple column accesses by changing column address inputs while the row remains active. The technique reduces repeated row-activation overhead imposed by the refresh and precharge cycles used in designs influenced by early work at companies like Intel Corporation and research at institutions such as Bell Labs and Fairchild Semiconductor.

Control timing involves signals analogous to those used in military and space computing systems by vendors like Honeywell and Raytheon for low-level hardware control, with the memory controller asserting CAS (Column Address Strobe) and RAS (Row Address Strobe) sequences in patterns familiar to system designers who used products from Digital Equipment Corporation and Sun Microsystems.

Performance Characteristics

Fast Page Mode DRAM yields lower effective column-access latency compared with non-page DRAM when memory access patterns exhibit spatial locality, benefiting processors with cache-miss streams similar to those observed in Intel 386 and Motorola 68030 workloads. Performance metrics depend on timing parameters produced by foundries such as GlobalFoundries and UMC (United Microelectronics Corporation), and on motherboard implementations by ASUS and Gigabyte Technology. Benchmarks of the era from research groups at Stanford University and industrial labs at Hewlett-Packard demonstrated improved sustained throughput in workloads with bursty, row-local accesses as seen in graphics subsystems designed by ATI Technologies and NVIDIA predecessors.

Latency and throughput are constrained by precharge time, column-address setup, and CAS latency; competing microarchitectures in gaming consoles like Sega and Nintendo exploited page-mode locality for sprite and tile rendering performance.

Comparison with Other DRAM Modes

Relative to single-access DRAM variants used in early mainframes at IBM, Fast Page Mode provided a clear advantage for sequential column reads. Compared with Extended Data Out DRAM and later Synchronous DRAM families used in systems by Sun Microsystems and Cray Research, Fast Page Mode lacks the synchronous clocking and pipelined burst semantics that characterize SDRAM and DDR generations promoted by organizations such as the JEDEC Solid State Technology Association. Unlike EDO DRAM, which extends data output to overlap with precharge for modest speed gains adopted by vendors like Micron Technology and Samsung Electronics, Fast Page Mode focuses on minimizing repeated row activations rather than extending output windows. Designers at Intel Corporation and chipset groups at VIA Technologies selected different modes depending on motherboard constraints and CPU frontend characteristics.

Applications and Historical Use

Fast Page Mode DRAM saw use in desktop PCs, workstations, and embedded systems produced by companies such as Compaq, Gateway 2000, HP, and Sun Microsystems during the 1980s and 1990s. It was common in graphics cards from firms like Matrox and in video memory architectures prior to the widespread adoption of dedicated VRAM and later GDDR by ATI Technologies and NVIDIA. Embedded controllers in telecommunications equipment built by Alcatel-Lucent and aerospace avionics by Boeing integrated Fast Page Mode parts for their predictable on-page performance. Educational and research platforms at institutions like MIT and Carnegie Mellon University used these DRAM devices in prototype systems and instruction kits.

Implementation and Timing Parameters

Key timing parameters for Fast Page Mode DRAM include tRAC (RAS to CAS delay), tRP (RAS precharge time), and tCAS (CAS latency) values specified by manufacturers such as Micron Technology and Samsung Electronics. Memory controllers—implemented in northbridge chips from Intel Corporation or discrete logic from National Semiconductor—manage signal sequencing with finite state machines described in hardware manuals from Xilinx and Altera (Intel FPGA). Typical device datasheets from firms like Hitachi and NEC Corporation listed access times in nanoseconds and recommended hold times for system designers at companies like Dell and IBM to tune BIOS parameters and timing tables. System integrators referenced platform-specific specifications from AMIBIOS and motherboard manuals to set refresh intervals and page-closing strategies that balance throughput and power consumption.

Category:Computer memory