Content-addressable memory

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 74 → Dedup 0 → NER 0 → Enqueued 0

| Content-addressable memory | |

|---|---|

Debabrattaj · CC BY-SA 4.0 · source | |

| Name | Content-addressable memory |

| Type | Memory system |

| Invented | 1960s |

| Inventor | Various |

| Industry | Computer hardware, Neuroscience |

Content-addressable memory

Content-addressable memory is a class of memory systems that enables retrieval by content rather than by address, offering parallel search capabilities and associative lookup. It intersects developments from Fairchild Semiconductor, IBM, Bell Labs, Stanford University, and Massachusetts Institute of Technology researchers, and has influenced hardware designs in companies such as Intel, AMD, Cisco Systems, and Xerox PARC. Its study spans contexts including electronic CAM devices, optical associative memories in laboratories like Lawrence Berkeley National Laboratory, and theoretical models in institutions such as Princeton University and California Institute of Technology.

Overview

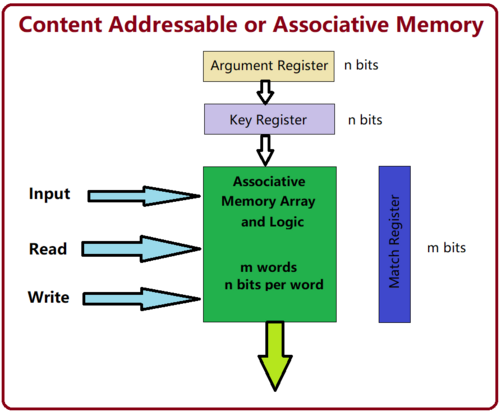

Content-addressable memory provides associative access where a search key is compared against stored data in parallel, enabling constant-time lookup under ideal conditions. Early demonstrations emerged alongside projects at IBM Research, Bell Labs, Texas Instruments, Hitachi, and NEC, while conceptual foundations drew on ideas from John von Neumann, Alan Turing, Claude Shannon, Norbert Wiener, and later computational theorists at Carnegie Mellon University. Practical CAM variants are produced by manufacturers including Micron Technology, Samsung Electronics, Broadcom, and Nvidia for use in networking and caching.

Architecture and Operation

CAM architectures typically integrate arrays of memory cells with comparator circuits and replacement logic, implemented in technologies developed at Intel Corporation fabrication facilities and research groups affiliated with TSMC, GlobalFoundries, and IBM Microelectronics. The operation uses parallel comparison hardware similar to circuits pioneered at Bell Laboratories and design methodologies taught at Massachusetts Institute of Technology and University of California, Berkeley. Control interfaces often adhere to standards advanced by IEEE, Internet Engineering Task Force, and European Telecommunications Standards Institute working groups, enabling integration with routers from Juniper Networks, Cisco Systems, and Arista Networks.

Types and Implementations

Implementations include binary CAM, ternary CAM (TCAM), content-addressable SRAM, and associative arrays realized in emerging memory technologies developed at Samsung, Intel Labs, IBM Research – Almaden, and startups spinouts from Stanford University and MIT Media Lab. TCAMs used in routers from Cisco Systems and Huawei Technologies support wildcard matching, while binary CAMs appear in cache-coherence schemes implemented by AMD and Intel in server platforms used by Amazon Web Services, Google Cloud, and Microsoft Azure. Research prototypes explore optical associative memories at Bell Labs, neuromorphic associative modules at IBM Watson Research Center and Intel Labs Neuromorphic Computing, and resistive memory CAMs from teams at IMEC and Tsinghua University.

Performance and Metrics

Key metrics for CAM include lookup latency, throughput, power-per-search, and density, measured in laboratories at Advanced Micro Devices, ARM Holdings, Qualcomm, and academic centers like University of Cambridge and ETH Zurich. Power consumption concerns link CAM performance to initiatives by Department of Energy and standards from JEDEC committees, while latency requirements drive adoption in infrastructure products from Cisco Systems and Arista Networks used in data centers run by Facebook, Twitter, and Netflix. Analytical models draw on complexity results from Alan Turing Institute collaborators and algorithmic frameworks advanced at Princeton University and Carnegie Mellon University.

Applications

CAMs serve in packet classification and routing tables in routers and switches by Cisco Systems, Juniper Networks, Huawei Technologies, and Arista Networks; in cache tag matching within processors from Intel, AMD, and ARM Holdings; and in database join accelerators developed at Oracle Corporation and research groups at Microsoft Research. Other applications include pattern matching in security appliances by Symantec and Palo Alto Networks, bioinformatics search accelerators in collaborations with Broad Institute and Wellcome Sanger Institute, and real-time signal processing for projects at NASA and European Space Agency.

Limitations and Challenges

Challenges include high power density, scaling limits in CMOS processes coordinated by TSMC and GlobalFoundries, cost per bit relative to DRAM and SRAM produced by SK Hynix and Micron Technology, and routing complexity addressed in standards meetings at IEEE 802 and IETF. Security and side-channel concerns have been noted in work from MIT Computer Science and Artificial Intelligence Laboratory, University of California, Berkeley, and University of Cambridge, while manufacturability and yield issues are topics in consortia involving SEMATECH and IMEC.

History and Development

Associative memory concepts trace to theoretical work by John von Neumann and early hardware experiments at Bell Labs, with commercial CAM products appearing from Texas Instruments, Fujitsu, and Hitachi in the 1980s and 1990s. The rise of high-speed networking in the 2000s spurred TCAM adoption in routers from Cisco Systems and Juniper Networks, and continued research has linked CAM evolution to neuromorphic initiatives at IBM Research, optical memory projects at Bell Labs and Lawrence Berkeley National Laboratory, and modern resistive memory efforts at IMEC and Tsinghua University.

Category:Computer memory