RISC architecture

Generated by Llama 3.3-70B

Generated by Llama 3.3-70BExpansion Funnel Raw 62 → Dedup 23 → NER 21 → Enqueued 19

| RISC architecture | |

|---|---|

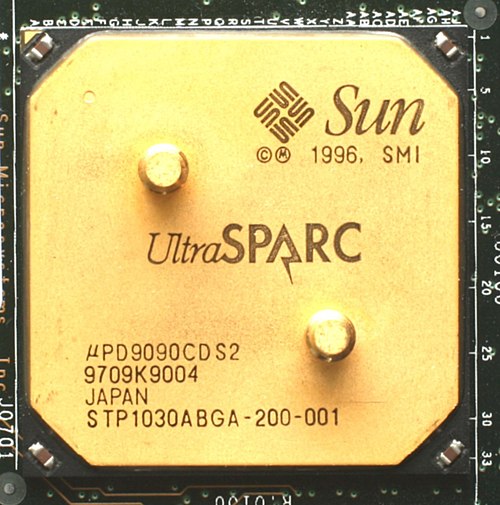

Konstantin Lanzet (with permission) · CC BY-SA 3.0 · source | |

| Name | RISC architecture |

RISC architecture is a type of computer CPU design that emphasizes simplicity, pipelining, and highly optimized instruction sets, as seen in the designs of John Cocke, IBM, and Stanford University. The development of RISC architecture was influenced by the work of David A. Patterson, Carlo Sequin, and Armando Stettner at University of California, Berkeley, and IBM Research. This design philosophy is in contrast to CISC architectures, which are more complex and have a larger number of instructions, as used in Intel Core and AMD Ryzen processors from Intel and AMD.

Introduction to RISC Architecture

RISC architecture is based on the idea of using simple, load/store instructions that can be combined to perform more complex tasks, as seen in the MIPS and ARM designs from MIPS and ARM. This approach is in contrast to CISC architectures, which use more complex instructions that can perform multiple tasks in a single clock cycle, as used in x86 and x86-64 processors from Intel and AMD. RISC architectures are often used in embedded systems, such as those found in Apple iPhone and Samsung Galaxy devices from Apple and Samsung, as well as in supercomputers, like those designed by Cray and IBM. The use of RISC architecture has also been explored in academic research at institutions like MIT, Stanford, and Cambridge.

History and Development

The development of RISC architecture began in the 1970s and 1980s, with the work of John Cocke and his team at IBM Research, which led to the development of the IBM 801 processor, a precursor to the POWER and PowerPC architectures. The concept of RISC architecture was further developed by David A. Patterson and his team at University of California, Berkeley, who designed the RISC-I and RISC-II processors, which were used in the SUN-1 and SUN-2 workstations from Sun. The RISC architecture was also influenced by the work of Carlo Sequin and Armando Stettner at University of California, Berkeley, and IBM Research. The development of RISC architecture was also influenced by the work of NSF-funded research projects, such as the MIPS project at Stanford, and the SPARC project at Sun.

Key Characteristics

RISC architectures have several key characteristics, including a load/store architecture, a simple instruction set, and a pipelined design, as seen in the ARM and MIPS designs. RISC architectures also typically use a register-register architecture, where instructions operate on registers rather than memory locations, as used in the IBM POWER and PowerPC architectures. This approach allows for faster execution of instructions and improved performance, as demonstrated by the benchmarks from SPEC and TPC. RISC architectures also often use a Harvard architecture, where the instruction and data memories are separate, as used in the ARM Cortex-A and MIPS32 processors.

Instruction Set Architecture

The instruction set architecture of a RISC processor is designed to be simple and efficient, with a focus on load/store instructions and ALU operations, as seen in the MIPS and ARM instruction sets. RISC instruction sets typically have a small number of instructions, often fewer than 100, as used in the RISC-V and SPARC instruction sets. This approach allows for faster execution of instructions and improved performance, as demonstrated by the benchmarks from SPEC and TPC. RISC instruction sets also often use a fixed-length instruction format, where all instructions are the same length, as used in the ARM and MIPS designs.

RISC vs CISC Architectures

RISC architectures are often compared to CISC architectures, which use more complex instructions that can perform multiple tasks in a single clock cycle, as used in x86 and x86-64 processors from Intel and AMD. RISC architectures are generally faster and more efficient than CISC architectures, but may require more instructions to perform complex tasks, as demonstrated by the benchmarks from SPEC and TPC. CISC architectures, on the other hand, are often more complex and have a larger number of instructions, but can perform complex tasks in a single clock cycle, as used in the Intel Core and AMD Ryzen processors. The choice between RISC and CISC architectures depends on the specific application and requirements, as seen in the designs of Apple, Google, and Microsoft.

Implementations and Examples

RISC architectures have been implemented in a wide range of processors, including the ARM and MIPS designs, which are used in embedded systems, such as those found in Apple iPhone and Samsung Galaxy devices from Apple and Samsung. RISC architectures are also used in supercomputers, like those designed by Cray and IBM, and in mainframe computers, such as those used by IBM and Unisys. Other examples of RISC architectures include the SPARC and PowerPC architectures, which are used in Sun and IBM systems, and the RISC-V architecture, which is an open-source RISC architecture developed by UC Berkeley and Google. The use of RISC architecture has also been explored in academic research at institutions like MIT, Stanford, and Cambridge. Category:Computer architecture