VHDL

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 69 → Dedup 0 → NER 0 → Enqueued 0

| VHDL | |

|---|---|

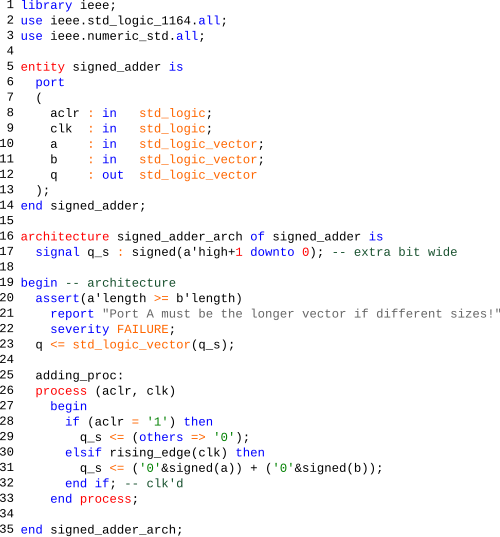

Vhdl_signed_adder.png: RevRagnarok

derivative work: Bernard Ladenthin · CC BY-SA 3.0 · source | |

| Name | VHDL |

| Paradigm | Hardware description language, concurrent and sequential modeling |

| Designer | Department of Defense (United States), IBM, Texas Instruments, Intermetrics |

| First appeared | 1980s |

| File extensions | .vhd, .vhdl |

| Influenced by | Ada (programming language), Pascal (programming language), ALGOL |

| Influenced | Verilog, SystemVerilog, SystemC, Bluespec |

VHDL is a hardware description language used to model digital systems at multiple abstraction levels. It enables engineers to describe structural, behavioral, and register-transfer level representations of electronic circuits and is widely adopted in industry and academia for designing integrated circuits and programmable logic devices. The language supports concurrent and sequential semantics, strong typing, and modular designs suitable for synthesis and formal verification workflows.

History

VHDL originated from a United States Department of Defense (United States) initiative in response to semiconductor project challenges, drawing technical input from companies such as IBM, Texas Instruments, and Intermetrics. Early standardization efforts led to adoption by the Institute of Electrical and Electronics Engineers and later revisions aligned with committees including IEEE 1076 Working Group activities. Major milestones include ANSI/IEEE standard publications and subsequent revisions that paralleled developments in related standards like IEEE 1164 and the emergence of competing languages exemplified by Verilog. The evolution of VHDL occurred alongside shifts in industry such as the rise of Xilinx, Altera, and the consolidation of EDA vendors like Cadence Design Systems and Synopsys that influenced synthesis and simulation tool support.

Language Overview

The language provides constructs for entity and architecture descriptions, enabling separation of interface and implementation reminiscent of modular designs from Ada (programming language) and Pascal (programming language). Types, subprograms, and packages allow encapsulation similar to mechanisms in Modula-2 and early ALGOL-derived languages. Concurrency is expressed via processes, concurrent signal assignments, and component instantiation, while sequential behavior appears inside processes and subprograms used by teams at companies such as Intel Corporation, Motorola, and National Semiconductor. Numeric and composite types support modeling of arithmetic units frequently designed by firms like NVIDIA and AMD (company). Standard libraries formalized by organizations including the IEEE provide multi-valued logic semantics that parallel needs addressed by developers at companies like Xilinx and Microsemi.

Design and Modeling Concepts

VHDL supports multiple abstraction levels: behavioral, register-transfer level, and structural descriptions used by designers at Apple Inc. and Qualcomm. Component instantiation and hierarchical design practices echo hardware engineering workflows at ARM Holdings and Broadcom Inc., facilitating reuse across teams at Texas Instruments and STMicroelectronics. Timing and concurrency semantics enable modeling of clock domains, reset schemes, and handshaking protocols familiar in projects such as PCI Express, USB, Ethernet, and processor cores like those from ARM Ltd.. Strong typing and explicit signal resolution functions aid in preventing integration errors encountered in collaborations between firms like Intel Corporation and Micron Technology. Verification strategies often pair VHDL models with assertions and checkers in environments maintained by vendors such as Mentor Graphics and research groups at Massachusetts Institute of Technology.

Simulation and Synthesis

Simulation of descriptions relies on event-driven simulators provided by companies including Cadence Design Systems, Mentor Graphics (now part of Siemens), and Aldec. Testbench methodologies commonly reference transaction-level verification techniques used in IBM research and enterprise workflows at Texas Instruments. Synthesis tools translate synthesizable subsets of the language into gate-level netlists for implementation on hardware platforms from Xilinx and Altera (now Intel FPGA). The interplay between synthesizable constructs and full language features mirrors tensions seen in standardization debates involving groups like IEEE Standards Association and corporate stakeholders including Synopsys and Cadence. Formal verification and equivalence checking between RTL and netlist often leverages tools developed by companies such as OneSpin Solutions and academic efforts at institutions like Stanford University.

Tooling and Ecosystem

A broad ecosystem of editors, simulators, synthesis tools, and verification frameworks supports the language, with commercial offerings from Synopsys, Cadence Design Systems, and Siemens EDA and open-source projects like GHDL and cocotb emerging from communities including contributors at Google and Red Hat. Education and training resources are provided by universities such as Carnegie Mellon University and University of California, Berkeley, and professional certification and standards discussion occur within organizations like IEEE and industry consortia including OpenHW Group. IP cores, reference designs, and vendor libraries from Xilinx, Intel FPGA, and Microchip Technology populate marketplaces and repositories used by startups incubated at places like Silicon Valley accelerators.

Applications and Use Cases

Engineers use the language for FPGA and ASIC design in domains ranging from consumer electronics by Sony and Samsung to telecommunications infrastructure by Huawei and Ericsson. Use cases include processor design and microarchitecture implementations inspired by work at ARM Holdings and RISC-V Foundation communities, high-speed I/O controllers in products by Broadcom Inc. and Marvell Technology, and mixed-signal control for automotive systems designed by Bosch and Continental AG. The language also underpins research projects in academic labs at MIT, ETH Zurich, and Imperial College London exploring novel architectures, hardware acceleration for machine learning studied by teams at NVIDIA and Google DeepMind, and hardware security initiatives developed in collaboration with institutes such as NIST.

Category:Hardware description languages