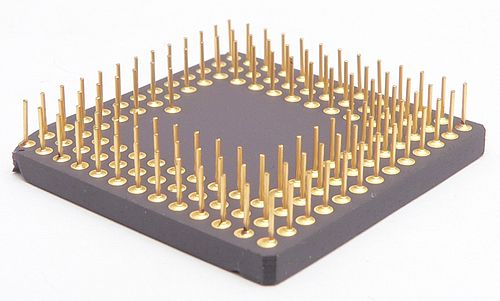

Pin Grid Array

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 62 → Dedup 0 → NER 0 → Enqueued 0

| Pin Grid Array | |

|---|---|

David Monniaux · CC BY-SA 3.0 · source | |

| Name | Pin Grid Array |

| Type | Integrated circuit packaging |

| Developer | Various semiconductor manufacturers |

| Introduced | 1970s |

| Use | Microprocessors, microcontrollers, ASICs |

Pin Grid Array

A Pin Grid Array package is a style of integrated circuit packaging that carries an array of electrical connection pins on the underside of a rectangular or square carrier, enabling high I/O counts for complex devices such as microprocessors and large-scale integration chips. It occupies a distinctive place among packaging families used by semiconductor firms such as Intel, IBM, AMD, Motorola and Texas Instruments and has been employed in platforms ranging from x86 desktop processors to embedded controllers for NASA missions. The format facilitated higher pin density and easier routing for motherboard designers at a time when surface-mount alternatives were less mature.

Overview

The package presents a regular two-dimensional grid of pins that mate with sockets or through-hole PCB pads; early adoption occurred in computing platforms developed by Digital Equipment Corporation and Sun Microsystems, and it was fundamental to computing ecosystems including VAX, SPARC, and early PC/AT clones. As packaging evolved, PGAs competed with land grid arrays used by vendors such as Intel for their Pentium series and with ball grid arrays promoted by consortia like the JEDEC committee. Manufacturers including Micron Technology and STMicroelectronics used PGAs for memory modules, discrete math coprocessors, and application-specific integrated circuits in systems developed at Bell Labs and research centers at MIT and Stanford University.

Design and Construction

Typical construction uses a ceramic, plastic, or organic substrate supporting a silicon die attached by die attach materials; the die is wire-bonded or flip-chip bonded to traces that fan out to an orthogonal pattern of through-hole pins. Companies such as Amphenol supplied sockets and connectors that mate with PGA packages, enabling insertion into motherboards designed by firms like ASUS or MSI. Thermal management often employs heat spreaders designed in collaboration with firms such as Cooler Master or Thermaltake and testing flows from fabs operated by TSMC and GlobalFoundries. The mechanical layout must meet standards set by bodies such as IPC (association), while electrical characteristics are specified to satisfy system integrators at HP and Dell.

Variants and Packaging Types

Multiple variants exist, including Ceramic Pin Grid Array (CPGA), Plastic Pin Grid Array (PPGA), Staggered Pin Grid Array (SPGA), Large Pin Grid Array (LPGA), and Zero Insertion Force (ZIF) socket-compatible designs; these were used across product families from AMD’s early Athlon to Intel’s pre-LGA cores. Some specialized derivatives include Dual-PGA constructs and high-density versions developed for supercomputing projects at Cray Research and national laboratories like Lawrence Livermore National Laboratory. Adapter modules often bridge PGA to Socket 462 or to legacy connectors used in systems from Compaq and Gateway.

Applications and Use Cases

PGAs were ubiquitous in desktop CPUs, workstations, and servers produced by IBM, Sun Microsystems, and many OEMs during the 1980s and 1990s, and they appear in network infrastructure equipment from Cisco Systems and Juniper Networks for certain control-plane processors. They were favored in prototype boards at institutions such as Caltech and ETH Zurich where reworkability via ZIF sockets aided iterative design. Embedded systems for aerospace and defense contractors like Lockheed Martin and Northrop Grumman also used PGA-packaged ASICs and radiation-hardened parts in projects coordinated with agencies such as DARPA and ESA.

Advantages and Disadvantages

Advantages include relatively straightforward cooling attachment compatible with third-party heatsinks sold by Noctua and easy user replaceability seen in enthusiast communities around Overclock.net and publications like Tom's Hardware. PGAs offered higher pin counts than traditional dual inline packages used in products from Intel’s early microprocessors and allowed for robust mechanical retention in server motherboards by Supermicro. Disadvantages encompass susceptibility to bent pins during handling, parasitic inductance for high-frequency signals that challenged radio-frequency designs at Qualcomm, and larger board real estate compared with modern surface-mount ball grid arrays embraced by Apple and Samsung Electronics.

Assembly, Testing, and Reliability

Assembly workflows include through-hole insertion, wave soldering, or hand placement followed by inspection techniques developed at National Institute of Standards and Technology and test flows used by fabs such as UMC. Burn-in, boundary-scan (JTAG) testing standardized by IEEE committees, and thermal cycling per standards from MIL-STD regimes govern reliability qualification for aerospace suppliers like Raytheon. Mechanical fatigue of pins and socket contacts led to lifecycle specifications adopted by server vendors such as Oracle (company) and cloud providers including Amazon Web Services for maintenance scheduling.

Historical Development and Evolution

The PGA form factor emerged in the 1970s and rose to prominence alongside microprocessor milestones like the Intel 386 and workstations from Sun Microsystems; through the 1990s it was a mainstay for desktop CPUs deployed by Dell and enthusiasts chronicled in AnandTech. As packaging technology advanced, land grid arrays and ball grid arrays, championed by organizations such as JEDEC and driven by companies including Intel and NVIDIA, displaced many PGA uses in favor of higher density and automated surface-mount assembly. Nevertheless, PGAs persisted in niches requiring socketed serviceability and retro-compatibility in heritage computing platforms maintained by museums such as the Computer History Museum.

Category:Semiconductor packages