P6 microarchitecture

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 70 → Dedup 17 → NER 9 → Enqueued 1

| P6 microarchitecture | |

|---|---|

| |

| Name | P6 microarchitecture |

| Developer | Intel Corporation |

| Introduced | 1995 |

| Successor | NetBurst |

| Process | 0.35 μm |

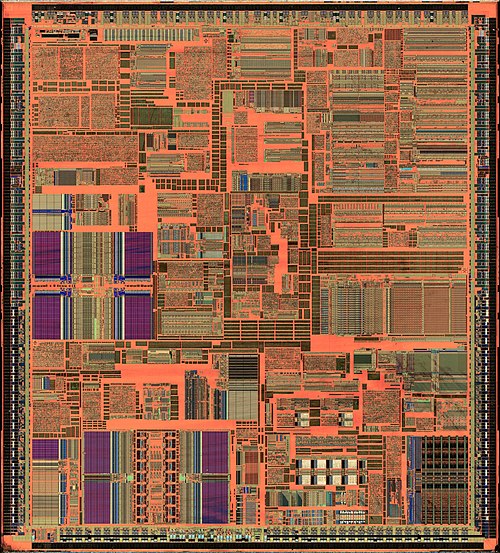

P6 microarchitecture The P6 microarchitecture was a 1990s high-performance x86 microprocessor core developed by Intel Corporation and introduced with the Pentium Pro in 1995. It combined out-of-order execution, speculative execution, and a decoupled front-end with a native RISC-like internal design to improve single-threaded instruction-level parallelism for server and desktop markets dominated by competitors such as Advanced Micro Devices and systems built by IBM and Sun Microsystems. The design influenced subsequent Intel families and informed academic work at institutions including Massachusetts Institute of Technology and Stanford University.

Overview

P6 originated as a project led by engineers at Intel Corporation's design centers, including teams based in Hillsboro, Oregon and Santa Clara, California. The core implemented a translation stage to convert complex x86 instruction set architecture operations into fixed-length micro-operations, adopting ideas similar to academic research from University of California, Berkeley, University of Illinois Urbana-Champaign, and papers presented at International Symposium on Computer Architecture conferences. Its release in the mid-1990s intersected with industry events such as the rise of Microsoft Windows NT servers and the growth of Linux deployments, positioning the microarchitecture for both workstation and enterprise use.

Design and features

The P6 introduced an internal micro-op pipeline and a register renaming scheme that reduced false dependencies, reflecting techniques discussed by researchers at Carnegie Mellon University and companies like DEC and Sun Microsystems. It featured a branch prediction unit informed by contemporary advances from researchers at University of Michigan and Princeton University, and used a speculative execution model comparable to designs from MIPS Technologies and ARM Holdings. The core supported a wide array of system vendors including Compaq, Hewlett-Packard, and Dell, and was optimized for operating systems such as Windows 95, Solaris, and Digital UNIX.

Pipeline and execution units

The pipeline separated instruction fetch, decode, and execution stages into a front-end and a back-end like architectures proposed at California Institute of Technology and in papers by John Hennessy and David Patterson. The front-end performed x86 decoding into micro-operations using a decoder array inspired by research from Bell Labs and the University of Toronto. The out-of-order scheduler dispatched micro-operations to multiple execution units — integer ALUs, floating-point units, and address generation units — paralleling execution strategies used in processors from IBM and Sun Microsystems. The microarchitecture included a reorder buffer and a retirement mechanism to commit results in program order, echoing designs from Advanced RISC Machines and academic groups at University of Cambridge.

Cache and memory subsystem

P6 implemented a multi-level cache hierarchy and a sophisticated memory subsystem influenced by work at Microsoft Research and Intel Research labs. The core integrated a first-level unified or split L1 cache and a larger on-package L2 cache in later iterations, a trend also seen in products from Motorola and SGI. The memory prefetch and coherency mechanisms were compatible with multiprocessor systems produced by Sequent Computer Systems and Unisys, and the platform supported system chipsets from vendors such as Intel Corporation's own chipset groups and partners including VIA Technologies and ALi Corporation.

Performance and benchmarks

At introduction, P6-based processors delivered strong performance on integer and floating-point workloads, outperforming contemporaries from Advanced Micro Devices in SPEC benchmarks and database workloads from vendors like Oracle Corporation and Sybase. Industry benchmarking groups such as Standard Performance Evaluation Corporation reported gains in IPC that benefited enterprise applications from SAP and scientific codes compiled with tools from GNU Project and compilers from Intel Corporation's compiler teams. The design's efficiency made it attractive for network and web server use in deployments by companies like Cisco Systems and Netscape Communications Corporation.

Implementations and derivatives

Implementations included the Pentium Pro, Pentium II, and early Pentium III variants, with packaging and integration by partners such as Intel Corporation's fabrication fabs in Ocotillo and other sites. Derivatives were adapted into multiprocessor server lines used by Sun Microsystems and enterprise systems from Hewlett-Packard and Dell EMC. The microarchitecture's principles were re-used in later Intel designs and influenced education and commercial projects at Texas Instruments and Fujitsu.

Legacy and impact on later architectures

P6's adoption of micro-op translation, register renaming, and out-of-order execution shaped subsequent Intel cores and inspired research at Massachusetts Institute of Technology, Stanford University, and industrial labs at IBM Research. Concepts from P6 informed the evolution of x86-64 implementations by AMD and later Intel families, and the core's techniques became standard teaching examples in curricula at Carnegie Mellon University and University of California, Berkeley. The microarchitecture's role in the server and desktop transition of the 1990s situates it alongside industry milestones like the growth of World Wide Web infrastructure and enterprise software ecosystems led by IBM and Microsoft.