NOR flash

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 53 → Dedup 0 → NER 0 → Enqueued 0

| NOR flash | |

|---|---|

Nrbelex · CC BY-SA 3.0 · source | |

| Name | NOR flash memory |

| Type | Non-volatile memory |

| Developer | Multiple semiconductor companies |

| Introduced | 1980s |

| Capacity | Kilobytes to gigabytes |

| Interface | Parallel, serial, SPI |

| Write cycles | 10^4–10^6 (typical) |

| Endurance | Variable |

| Access | Random-access read, block erase |

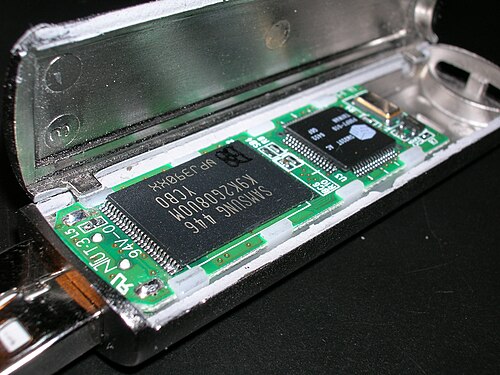

NOR flash NOR flash is a type of non-volatile memory introduced in the 1980s for code storage and execute-in-place scenarios, used widely in embedded systems, consumer electronics, aerospace, and telecommunications. It combines transistor-level designs from early MOSFET research with commercial manufacturing practices pioneered by semiconductor companies and standards bodies, enabling persistent storage with random-access read capability and block-based erase semantics.

Overview

NOR flash was developed concurrently with other memory technologies during a period influenced by research at institutions such as Bell Labs, industrial efforts by firms like Intel Corporation and AMD, and standards work involving organizations like JEDEC Solid State Technology Association. Its architecture derives from charge-trapping and floating-gate transistor inventions connected to earlier work at Fairchild Semiconductor and Texas Instruments. The productization of NOR involved design trade-offs explored in conferences such as the International Solid-State Circuits Conference and supply-chain decisions by manufacturers including Micron Technology, Samsung Electronics, and STMicroelectronics.

Architecture and Operation

The core elements of NOR flash are floating-gate transistors and interconnects patterned using lithography techniques developed by companies like ASML Holding and equipment suppliers such as Applied Materials. Arrays are organized into bit lines and word lines reminiscent of memories described in textbooks from Massachusetts Institute of Technology and research labs at Stanford University. Read operations permit byte-addressable random access similar to architectures discussed in work from Intel Corporation and ARM Holdings for embedded processors, while erase operations occur at block granularity influenced by standards from JEDEC Solid State Technology Association and implementation choices by vendors like NXP Semiconductors.

Manufacturing and Technologies

Fabrication of NOR devices involves processes and equipment from firms such as TSMC, GlobalFoundries, and UMC, leveraging process nodes described in publications from IEEE venues and capital equipment from ASM International. Process integration includes gate-stack engineering, dielectric deposition techniques associated with research at IMEC, and implantation steps traced to earlier semiconductor advances at Bell Labs. Packaging and testing frequently use facilities run by contract manufacturers like Foxconn and ASE Technology Holding to meet qualification standards employed by customers including Boeing, Lockheed Martin, and General Dynamics for avionics and defense markets.

Performance and Reliability

NOR devices are characterized by deterministic read latency and execute-in-place capability that suit microcontroller use cases highlighted by firms such as Microchip Technology, Texas Instruments, and NXP Semiconductors. Endurance, retention, and failure modes are analyzed in standards and test suites developed by JEDEC Solid State Technology Association and reported in reliability studies from laboratories at Sandia National Laboratories and Argonne National Laboratory. Failure mechanisms include charge loss and oxide degradation topics investigated in academic work from University of California, Berkeley and University of Illinois Urbana-Champaign, and mitigations rely on error-correcting codes and wear-leveling strategies implemented by device vendors like Winbond Electronics and Cypress Semiconductor.

Use Cases and Applications

NOR flash is commonly used for firmware storage, boot ROMs, and code shadowing in embedded platforms produced by companies such as Siemens, Bosch, and Hitachi. Industries employing NOR include automotive systems designed by Bosch and Continental AG, aerospace programs at Lockheed Martin and Airbus, and telecommunications equipment from Ericsson and Huawei Technologies. The technology supports applications requiring read stability and single-byte access in products from Garmin, Sony Corporation, and Panasonic.

Comparison with NAND Flash

Comparisons with NAND flash often involve trade-offs between random-access read performance and density economies driven by producers like Samsung Electronics and SK Hynix. NAND, promoted by firms including Toshiba and Western Digital, offers higher bit density and lower cost per bit but requires wear leveling and complex controllers like those described by developers at Intel Corporation and ARM Holdings for flash translation layers. NOR’s strengths in execute-in-place and deterministic reads contrast with NAND’s suitability for mass storage in solutions from companies such as SanDisk and Seagate Technology.

Future Developments and Trends

Future directions draw on research agendas at organizations such as IMEC, CEA-Leti, and academic centers like Massachusetts Institute of Technology and Stanford University exploring scaling limits, alternative materials, and 3D integration approaches used by foundries like TSMC and Samsung Electronics. Industry roadmaps coordinated by JEDEC Solid State Technology Association and investment decisions by firms such as Intel Corporation and Micron Technology will shape advances including embedded multi-die packaging, improved endurance algorithms by vendors like Cypress Semiconductor, and hybrid memory designs influenced by research at University of Cambridge and ETH Zurich.

Category:Non-volatile memory