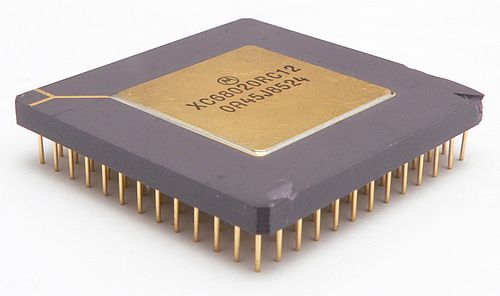

Motorola 68020

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 55 → Dedup 0 → NER 0 → Enqueued 0

| Motorola 68020 | |

|---|---|

David Monniaux · CC BY-SA 3.0 · source | |

| Name | Motorola 68020 |

| Manufacturer | Motorola |

| Produced | 1984–1990s |

| Family | 68000 series |

| Arch | 32‑bit CISC |

| Cppu | 32 |

| Address | 32‑bit |

| Data | 32‑bit |

| Predecessor | 68010 |

| Successor | 68030 |

Motorola 68020 The Motorola 68020 is a 32‑bit microprocessor introduced by Motorola in 1984 as part of the 68000 family. It provided a fully 32‑bit external and internal datapath, a richer instruction set, and enhanced addressing modes that accelerated systems ranging from workstations to embedded controllers. The 68020 influenced designs in companies and institutions across the computing industry and appeared in systems alongside processors from Intel, Zilog, and IBM collaborators.

Introduction

The 68020 was developed at Motorola’s semiconductor groups in Austin and Phoenix, following design lineage from the 68000 and 68010 and preceding the 68030 and 68040 generations. It competed in markets served by companies such as Intel, Advanced Micro Devices, National Semiconductor, Zilog, and Motorola's own affiliates. Early adopters included workstation manufacturers like Sun Microsystems, Silicon Graphics, and Apollo Computer, and it was used by military contractors, telecommunications firms, and academic laboratories at institutions such as MIT and Stanford University.

Architecture and Features

The chip implemented a 32‑bit Arithmetic Logic Unit and 32‑bit general‑purpose registers, extending concepts from earlier designs by engineers influenced by work at Bell Labs and processor teams interacting with researchers from UC Berkeley. Notable features included a paged memory management option, a coprocessor interface compatible with the IEEE 754 floating‑point standard via the Motorola 68881 and 68882 numeric coprocessors, and a richer instruction set architecture reminiscent of work by teams at DEC and Hewlett-Packard. The 68020 supported complex addressing modes used by software from companies like Microsoft and Apple Computer and integrated new instructions for bit manipulation and loop control that benefited compilers from vendors such as GCC and Watson Research Center teams at IBM.

Performance and Implementations

Performance benchmarks placed the 68020 favorably against contemporaries from Intel Corporation and Motorola rivals in integer workloads, while numeric performance often depended on pairing with the 68881/68882 coprocessors used in systems by NeXT, Commodore-Amiga vendors like Commodore, and graphics firms such as Silicon Graphics. Implementations appeared in motherboards from manufacturers like DEC, HP, and third‑party OEMs supplying NASA centers and defense contractors including Lockheed Martin and Raytheon. Compiler and operating system support grew from communities around Unix System V, BSD, and proprietary OS efforts by Apple and Atari Corporation.

Use in Systems and Applications

The 68020 powered workstations from Sun Microsystems and Silicon Graphics, personal computers from Apple Computer variants, laser printers from Xerox and Hewlett-Packard, and embedded controllers in networking equipment by Cisco Systems and 3Com. It was integrated into arcade and console hardware alongside custom ASICs designed by studios such as Konami and Capcom. Scientific instrumentation at laboratories including CERN and observatories like Palomar Observatory used 68020‑based controllers, while industrial automation companies such as Siemens and ABB deployed it in process control systems.

Variants and Derivatives

Motorola and licensees produced multiple clock‑speed grades and packaging options, with derivatives that incorporated on‑chip caches and improved memory management leading to successors like designs influenced by teams at Motorola and external partners including Fujitsu and Hitachi. Embedded versions appeared in telecommunications exchanges designed by Nortel and Ericsson, and custom ASIC integrations by firms like Motorola Semiconductor divisions supplied variants for automotive systems from Bosch and avionics projects by Honeywell.

Legacy and Impact on Computing

The 68020 helped cement 32‑bit architecture expectations in workstation and embedded markets, influencing later architectures from Sun Microsystems with SPARC, from Intel with the i386 family, and research groups at Carnegie Mellon University and Stanford University exploring RISC principles. Its instruction extensions and coprocessor model informed floating‑point handling in subsequent CPUs from Motorola and competitors such as AMD and Cyrix. Educational courses at institutions like Georgia Tech and University of Illinois Urbana–Champaign used 68020 architecture material in computer architecture curricula, and its role in pioneering multimedia, scientific, and telecommunications applications contributed to technology histories chronicled by museums such as the Computer History Museum.