JFET

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 53 → Dedup 0 → NER 0 → Enqueued 0

| JFET | |

|---|---|

Vector version: VectorVoyager

PNG version: Rparle at English Wikipedia · CC BY-SA 3.0 · source | |

| Name | Junction Field-Effect Transistor |

| Type | Semiconductor device |

| Introduced | 1950s |

| Inventor | William Shockley |

| Terminals | Gate; Source; Drain |

| Operation | Voltage-controlled current source |

JFET

The junction field-effect transistor is a three-terminal semiconductor device that controls current via a reverse-biased p–n junction. It appears in the evolution of solid-state electronics alongside vacuum tubes, bipolar junction transistors, and metal–oxide–semiconductor field-effect transistors, and has been used in analog circuits, radio frequency receivers, and sensor front ends. Key historical figures and institutions contributed to its development, and it remains relevant in teaching, hobbyist projects, and certain low-noise commercial applications.

Introduction

The JFET concept emerged during the same era as contributions from William Shockley, John Bardeen, and Walter Brattain at Bell Labs, and it forms part of the family of field-effect devices that also includes devices developed by Robert Noyce and Gordon Moore at Fairchild Semiconductor. Early demonstrations linked to researchers at Bell Telephone Laboratories and patent activity involving industrial actors like RCA and Texas Instruments shaped its commercialization. The device sits historically between innovations such as the Audion legacy of Lee de Forest and the integrated circuit breakthroughs epitomized by the Intel 4004.

Structure and Operation

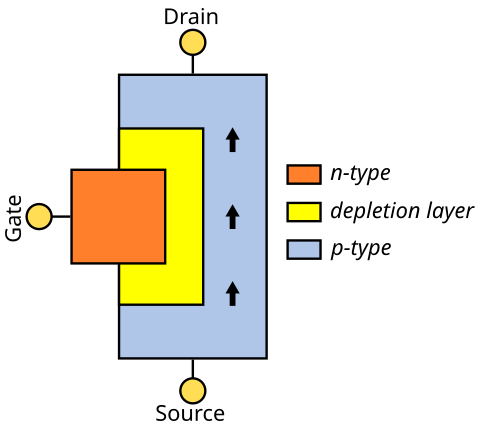

A JFET consists of a narrow channel of one semiconductor type with diffused p-type or n-type regions forming the gate junctions, fabricated using processes pioneered at Fairchild Semiconductor and Intel. The basic three-terminal arrangement—gate, source, and drain—allows control of channel conductance by a voltage that reverse-biases the gate–channel p–n junction, reminiscent of rectifying behavior studied by Leo Esaki and others. In operation the device exhibits pinch-off, depletion-region expansion, and saturation phenomena analogous to behaviors examined in semiconductor physics experiments at institutions like MIT and Stanford University. The device symbol and biasing conventions are widely taught in courses associated with Massachusetts Institute of Technology and California Institute of Technology curricula.

Electrical Characteristics

Key parameters include drain–source saturation current, transconductance, pinch-off voltage, and gate–source leakage, metrics similar to those reported in device characterizations from IEEE conferences and journals. The I–V curves show a channel-current plateau beyond pinch-off, comparable to descriptions in classics by Horowitz and Hill and measurement techniques developed at Bell Labs and National Institute of Standards and Technology. Noise performance and thermal dependence were analyzed in studies involving laboratories at Bell Telephone Laboratories and academic groups at University of California, Berkeley; such work influenced low-noise amplifier designs used in equipment by manufacturers like Tektronix and Rohde & Schwarz.

Types and Variants

Variants include n-channel and p-channel polarity devices, dual-gate topologies, and lateral versus vertical geometries; these families evolved in parallel with complementary technologies from Motorola and Philips. Specialized forms—such as depletion-mode MESFET cousins and heterostructure FETs—reflect cross-fertilization with work at AT&T Bell Laboratories and research centers like IBM Research. Dual-gate JFETs were employed in RF front ends developed by teams at BBC Research and military contractors involved with projects at Sandia National Laboratories.

Applications

JFETs have been used in input stages of operational amplifiers by companies like National Semiconductor and in radio-frequency mixers and preamplifiers for receivers developed at Collins Radio Company and Harris Corporation. They appear in audio equipment produced by firms such as Fender Musical Instruments Corporation and Marshall Amplification for low-distortion, high-impedance inputs. Scientific instrumentation from organizations like CERN and observatories associated with Harvard University and Princeton University has employed JFETs for charge-sensitive preamplifiers and low-noise detectors. Hobbyist platforms and educational kits from institutions like Make: and Arduino communities also utilize JFETs for teaching analog electronics fundamentals.

Design and Biasing Considerations

Designers examine gate leakage, source degeneration, and bias networks using classical techniques outlined by authors associated with IEEE Spectrum and textbooks from McGraw-Hill. Biasing schemes often reference standards and models developed in academic groups at University of Illinois, and practical design choices are influenced by component databases maintained by distributors like Digi-Key and Mouser Electronics. Thermal management and device matching for differential stages invoke practices used in precision amplifier projects at Bell Labs and measurement protocols established by National Instruments.

Fabrication and Packaging

JFET fabrication leverages diffusion, ion implantation, and masking methods refined at fabrication facilities such as those operated by Fairchild Semiconductor, Intel, and Texas Instruments. Packaging ranges from through-hole metal cans used historically by Collins Radio Company to modern surface-mount packages produced by STMicroelectronics and Analog Devices. Reliability testing and qualification draw on standards from organizations including JEDEC and IEC, while automated test equipment from companies like Advantest and Teradyne is used for production verification.

Category:Transistors