DDR5 SDRAM

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 50 → Dedup 3 → NER 2 → Enqueued 2

| DDR5 SDRAM | |

|---|---|

| |

| Name | DDR5 SDRAM |

| Type | Synchronous dynamic random-access memory |

| Generation | DDR5 (fifth generation) |

| Predecessor | DDR4 SDRAM |

| Developer | JEDEC |

| Introduced | 2020s |

| Capacity | up to 128 GB per DIMM (module-dependent) |

| Voltage | 1.1 V (typical) |

| Data rate | 3200–8400 MT/s (market range) |

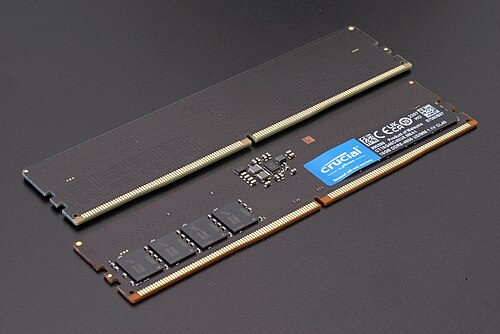

DDR5 SDRAM DDR5 SDRAM is the fifth-generation double data rate synchronous dynamic random-access memory developed to increase bandwidth and capacity for modern computing platforms. It was standardized by JEDEC and adopted by major manufacturers and system vendors to meet demands from servers, workstations, gaming, and AI acceleration. DDR5 focuses on higher data rates, improved power efficiency, and on-die features to support scaling beyond DDR4.

Overview

DDR5 emerged as the successor to DDR4 through a JEDEC standardization process involving companies such as Samsung Electronics, SK Hynix, Micron Technology, Intel Corporation, and AMD. Major platform launches by Intel Corporation and Advanced Micro Devices integrated DDR5 support, with server adoption driven by vendors including Dell Technologies, Hewlett Packard Enterprise, Lenovo Group, and hyperscalers like Amazon Web Services, Microsoft Azure, and Google Cloud Platform. Memory module and subsystem design also involved firms such as Kingston Technology, Corsair, G.Skill, and Crucial Technology. The transition paralleled previous generational shifts seen with DDR3 and DDR4, influenced by market cycles shaped by events involving TSMC, GlobalFoundries, and semiconductor demand spikes occasioned by the COVID-19 pandemic.

Technical specifications

Key specifications were defined by JEDEC committee JESD79-5 revision work, aligning signaling, timing, and I/O parameters used by system integrators such as ASUS, Gigabyte Technology, and MSI. Nominal voltage dropped to 1.1 V, similar to power-reduction trends set by Intel Xeon and AMD EPYC server families. Transfer rates were specified starting at 3200 MT/s and scaling upward to 8400 MT/s on roadmap projections used by suppliers like Samsung Electronics and SK Hynix. Module capacities leverage advances in die stacking and 3D packaging used by Micron Technology and packaging houses like ASE Technology Holding. Standard DIMM and SODIMM form factors support capacities up to and beyond 64 GB per module, with ECC and registered options for enterprise platforms from Broadcom Inc. and memory controller implementations found in ARM Holdings-based designs.

Architecture and features

DDR5 introduced architectural changes including doubled banks and bank groups, on-die ECC, and a dual-channel DIMM architecture per module—features developed with contributions from memory IP providers and subsystem integrators. On-die ECC reduces soft error rates using internal correction similar in intent to techniques by IBM. The dual independent 32-bit subchannels per DIMM enable finer-grained access patterns favored by server workloads on AMD EPYC and Intel Xeon Scalable platforms. Power management shifted partly on-module with the addition of a power management integrated circuit (PMIC), a design seen in collaboration with power-IC suppliers like Texas Instruments and Analog Devices. Address and command bus timing and the move toward higher prefetch depths reflect engineering trends also present in prior innovations by JEDEC Solid State Technology Association.

Performance and benchmarks

Benchmarks comparing DDR5 to DDR4 show higher peak bandwidth and improved sustained throughput in memory-bound workloads from applications in databases, scientific computing, and AI training using accelerators by NVIDIA Corporation and AMD Instinct. Performance gains depend on memory controller implementations by CPU vendors such as Intel Corporation and Advanced Micro Devices and on interconnects like PCI Express generations used by GPUs and NVMe storage from firms like Samsung Electronics and Western Digital. Synthetic benchmarks from organizations including SPEC and industry labs show latency increases in some access patterns offset by throughput gains; real-world application benchmarks by cloud providers (Amazon Web Services, Microsoft Azure) and research centers illustrate mixed outcomes depending on workload concurrency, NUMA topology, and DIMM population.

Compatibility and standards

Backward electrical compatibility with DDR4 is not present; platform-level support required CPU and chipset updates from Intel Corporation (client and server chipsets) and AMD platform controllers. JEDEC-driven interoperability testing involved system OEMs such as Dell Technologies and Lenovo Group plus motherboard manufacturers ASUS and Gigabyte Technology. Memory training procedures (e.g., memory reference code used in firmware by vendors like American Megatrends and Insyde Software) and SPD/EEPROM definitions ensure cross-vendor module recognition. Enterprise features such as registered DIMM (RDIMM) and load-reduced DIMM (LRDIMM) variants follow module standards adopted by chassis and server vendors including Supermicro and HPE.

Manufacturing and market adoption

Production ramp-up was led by major fabs and IDM companies including Samsung Electronics, SK Hynix, Micron Technology, and supported by foundries like TSMC for peripheral logic. Module assembly by contract manufacturers such as Foxconn and packaging by ASE Technology Holding enabled supply to channel brands Kingston Technology, Corsair, and G.Skill. Market adoption accelerated with desktop and mobile platform releases by Intel Corporation and AMD, and enterprise adoption tracked server refresh cycles in data centers operated by Amazon Web Services, Google Cloud Platform, and large research institutions. Pricing dynamics reflected DRAM industry cycles influenced by inventory management by large buyers and geopolitical factors involving South Korea and Taiwan semiconductor ecosystems.

Security and reliability mechanisms

DDR5 includes on-die ECC to detect and correct certain memory errors and supports module-level ECC and address parity to enhance reliability for enterprise systems designed by IBM and server OEMs. Error mitigation strategies integrate with system firmware and OS-level features provided by vendors like Microsoft and Red Hat to report and handle memory errors. Supply chain security and hardware root-of-trust concerns intersect with initiatives by standards organizations such as NIST and industry consortia including Trusted Computing Group. Reliability testing and qualification use methodologies from labs like UL and certification programs overseen by JEDEC members.

Category:Computer memory