DDR5

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 53 → Dedup 0 → NER 0 → Enqueued 0

| DDR5 | |

|---|---|

| |

| Name | DDR5 |

| Introduced | 2020 |

| Type | Synchronous dynamic random-access memory (SDRAM) |

| Predecessor | DDR4 |

| Successor | DDR6 |

| Designer | JEDEC |

| Used in | Personal computers, servers, workstations, laptops |

DDR5.

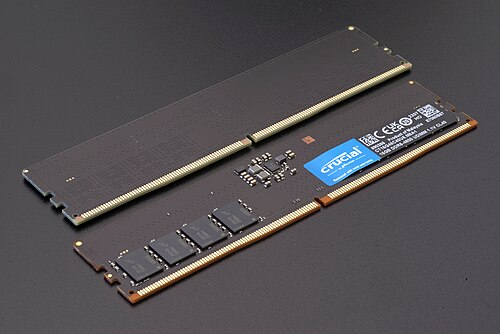

DDR5 is the fifth-generation double data rate synchronous dynamic random-access memory standard defined by the JEDEC Solid State Technology Association. It succeeds DDR4 SDRAM and precedes DDR6, aiming to increase per-module capacity, data rate, and power efficiency for contemporary platforms such as Intel and AMD microarchitectures in client and enterprise systems. The specification influences major manufacturers including Samsung Electronics, Micron Technology, SK Hynix, and Kingston Technology and affects ecosystems around Windows 11, Linux kernel, and hyperscale deployments by Amazon Web Services and Microsoft Azure.

Overview

DDR5 was developed within the standards process governed by JEDEC committees to address rising demands from high-performance computing projects like HPC clusters used at facilities such as Oak Ridge National Laboratory and research programs at CERN. Early public demonstrations involved partners including Intel Corporation and AMD during platform launches that echo previous transitions such as DDR3 SDRAM to DDR4 SDRAM. Major manufacturing roadmaps from TSMC-class fabs and memory foundries such as Samsung Electronics and SK Hynix supported commercial availability for consumer devices and data-center grade modules used by organizations like Google and Meta Platforms.

Technical Specifications

The DDR5 specification increases nominal transfer rates beyond those standardized for DDR4 SDRAM, enabling per-pin data rates starting at 3200 MT/s and scaling to 6400 MT/s and beyond in later JEDEC updates. Module density advances allow single-module capacities reaching 128 GB and larger through stacked die techniques employed by Micron Technology and Samsung Electronics. Voltage rails moved towards a lower DIMM supply, while introducing a 1.1 V nominal supply and an integrated power management integrated circuit (PMIC) on DIMMs, a design influenced by power strategies used in ARM-based server projects and mobile designs from Qualcomm. Error mitigation is supported via on-die ECC, complementary to system-level ECC typical in Dell Technologies and Hewlett Packard Enterprise servers.

Architecture and Features

DDR5 changes internal channel architecture by splitting each DIMM into two independent 32-bit subchannels (or 40-bit with ECC), resembling channelization strategies seen in multi-channel architectures from Intel and AMD. The addition of per-DIMM PMIC simplifies motherboard power routing, a technique reminiscent of power management evolution in NVIDIA GPU modules and Apple system designs. On-die ECC enhances yield and reliability using methods similar to those found in enterprise NAND solutions from Western Digital and Seagate Technology. Command/address bus and burst lengths were revised, and new training sequences were introduced, reflecting signaling advances present in high-speed interconnects such as PCI Express evolutions and PHY management like that in Broadcom switching silicon.

Performance and Comparisons

Benchmarks comparing DDR5 and DDR4 across platforms from Intel and AMD show higher peak bandwidth for DDR5, with latency behavior dependent on clocking and memory controller implementation seen in chipsets from ASUS and MSI. For workloads typical of databases and in-memory analytics used by Oracle Corporation and SAP SE, DDR5’s greater throughput and capacity provide measurable gains, while gaming and real-time rendering tasks common in Valve and Epic Games ecosystems show mixed results influenced by GPU-memory balance seen in NVIDIA GeForce and AMD Radeon designs. Data-center operators like Equinix evaluate total cost of ownership considering power per bit and module densities, analogous to storage TCO assessments by NetApp.

Adoption and Market Impact

Major original equipment manufacturers such as Dell Technologies, HP Inc., and Lenovo integrated DDR5 into server and client product lines following launch windows from Intel and AMD. Cloud providers including Amazon Web Services and Microsoft Azure planned migrations aligned with silicon roadmaps and procurement cycles similar to prior transitions in virtualization platforms like VMware. Memory suppliers Samsung Electronics, SK Hynix, Micron Technology, and module makers like Kingston Technology and Corsair scaled production, affecting supply chains across fabs such as TSMC and packaging services used by ASE Technology Holding. Market dynamics influenced pricing in the aftermarket tracked by firms like IDC and Gartner.

Implementation and Compatibility

DDR5 adoption requires platform support in memory controllers integrated into CPUs and chipsets developed by Intel Corporation and AMD, and BIOS/UEFI firmware updates from vendors such as American Megatrends and Insyde Software. Motherboard manufacturers including ASUS, MSI, and Gigabyte Technology updated PCB layouts, routing guidelines, and power delivery subsystems to accommodate PMIC-equipped DIMMs and revised timing parameters, mirroring board-level changes seen in transitions like DDR3 to DDR4. Backward compatibility is not provided at the DIMM level; system integrators coordinate SKU transitions similarly to previous migrations managed by enterprise procurement teams at Dell Technologies and Hewlett Packard Enterprise.

Category:Computer memory standards