Advanced Encryption Standard

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 75 → Dedup 0 → NER 0 → Enqueued 0

| Advanced Encryption Standard | |

|---|---|

| |

| Name | Advanced Encryption Standard |

| Type | Block cipher |

| Designers | Vincent Rijmen, Joan Daemen |

| Publish date | 2001 |

| Key size | 128, 192, 256 bits |

| Block size | 128 bits |

| Structure | Substitution–permutation network |

Advanced Encryption Standard is a symmetric-key block cipher standardized to protect digital information across diverse systems. It succeeded earlier algorithms after an open competition and is widely integrated in protocols, products, and regulatory frameworks used by institutions and enterprises. Its selection influenced cryptographic practice, interoperability, and research in applied cryptography, shaping implementations from embedded devices to cloud platforms.

History and development

The selection process originated with a public call by the National Institute of Standards and Technology following concerns about the longevity of Data Encryption Standard; the competition drew submissions from cryptographers associated with institutions such as IBM, RSA Security, and academic groups led by individuals like Mitsuru Matsui and Eli Biham. The Rijndael algorithm, designed by Vincent Rijmen and Joan Daemen while connected with Belgian research networks and universities, advanced through evaluation rounds involving reviewers from European Union research programs, the Cryptographic Module Validation Program, and experts affiliated with MIT, University of California, Berkeley, and Technische Universiteit Eindhoven. Finalization in 2001 coincided with policy discussions involving the United States Congress and guidance from agencies such as the National Security Agency and standards bodies including the International Organization for Standardization and the Internet Engineering Task Force.

Algorithm design and structure

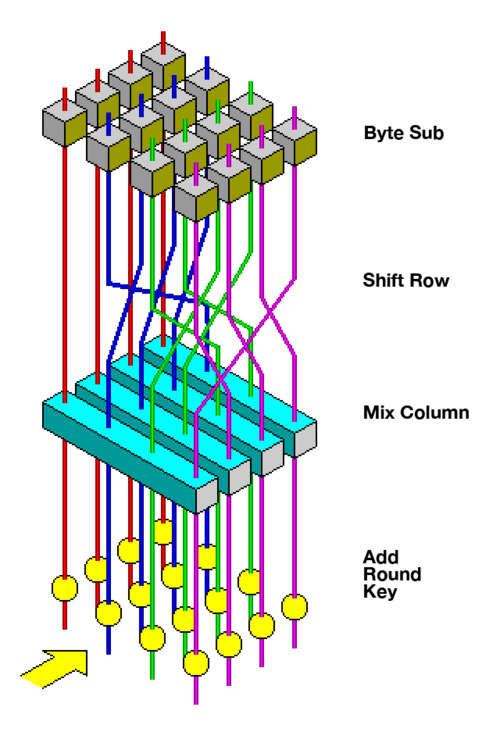

Rijndael’s design employs a substitution–permutation network built on byte-oriented operations and a 128-bit block size; the round function combines a nonlinear S-box with linear diffusion layers inspired by mathematical constructs studied at KU Leuven and other European centers. The cipher’s state matrix and operations—AddRoundKey, SubBytes, ShiftRows, and MixColumns—were influenced by algebraic research from groups at École Polytechnique Fédérale de Lausanne, Royal Holloway, University of London, and cryptanalytic work by scholars such as Adi Shamir and Claude Shannon who provided foundational theory employed in its security proofs. Designers balanced simplicity, low memory footprint, and resistance to ciphertext-only and differential attacks evaluated during review by teams at INRIA, NIST, and University of Cambridge.

Key sizes, modes, and implementations

AES specifies three key lengths—128, 192, and 256 bits—paralleling recommendations from organizations like the European Commission and the U.S. Department of Defense for different assurance levels. Practical deployment uses block cipher modes standardized in documents authored by working groups within the Internet Engineering Task Force, including Cipher Block Chaining and Galois/Counter Mode; implementations appear in libraries maintained by projects such as OpenSSL, LibreSSL, BoringSSL, and cryptographic toolkits from vendors like Microsoft and Apple. Hardware realizations are integrated into processors designed by Intel, ARM Holdings, and AMD as AES instruction set extensions, while embedded deployments appear in devices from Cisco Systems and Qualcomm.

Security analysis and cryptanalysis

Extensive cryptanalytic evaluation by researchers at institutions including SRI International, École Normale Supérieure, Technische Universität Darmstadt, and independent cryptographers such as Kilian Valk, Alex Biryukov, and Johannes Buchmann tested resistance to differential, linear, and algebraic attacks. No practical full-key break has been demonstrated against the standard; reduced-round versions have been exploited in theoretical studies by teams at TU Graz and University of Luxembourg. Side-channel attacks, including power analysis and timing attacks, prompted countermeasure research from groups at University of Cambridge, Bar-Ilan University, and industrial labs at IBM Research and Google.

Performance and hardware/software optimization

Software implementations benefit from instruction set support such as the AES-NI extension introduced by Intel and adopted by AMD, enabling faster iterations in servers used by providers like Amazon Web Services and Google Cloud Platform. Parallelizable modes like GCM allow throughput scaling on multicore systems designed by NVIDIA and accelerators from Xilinx and Altera; low-power microcontroller implementations have been demonstrated by researchers at Fraunhofer Society and companies such as STMicroelectronics for IoT products. Constant-time programming techniques advocated by teams at Microsoft Research and OpenBSD mitigate timing leakage; hardware masking and glitch resistance are topics in publications from TU Kaiserslautern and University of Tokyo.

Standardization, adoption, and applications

AES was adopted in national and international standards promulgated by NIST, ISO/IEC, and regulatory frameworks overseen by agencies such as the Federal Information Processing Standards program; industry certifications include those administered by the Common Criteria and the Cryptographic Module Validation Program. It underpins protocols standardized by the Internet Engineering Task Force and organizations like IEEE for secure communications in products from Cisco Systems, Siemens, and Ericsson. AES secures data at rest and in transit across sectors involving financial institutions like Visa and Mastercard, cloud providers including Microsoft Azure, and critical infrastructure vendors working with Siemens and Schneider Electric.

Category:Cryptographic algorithms