AMD64

Generated by GPT-5-mini

Generated by GPT-5-miniExpansion Funnel Raw 63 → Dedup 3 → NER 2 → Enqueued 0

| AMD64 | |

|---|---|

| |

| Name | AMD64 |

| Designer | Advanced Micro Devices |

| Designfirm | Advanced Micro Devices |

| Introduced | 2003 |

| Architecture | x86-64 |

| Bits | 64-bit |

| Extensions | SSE, SSE2, SSE3, SSE4, AVX, AVX2 |

| Code | x86-64 |

AMD64.

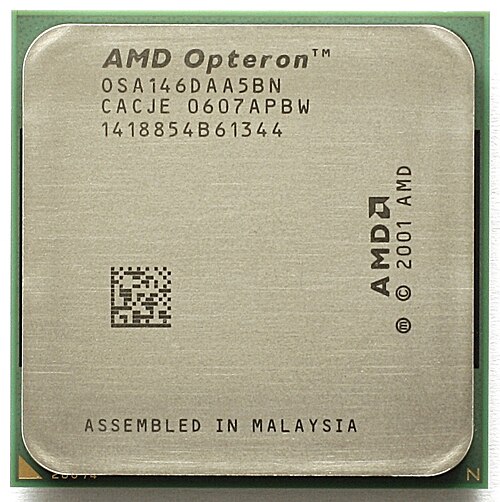

AMD64 is a 64-bit microprocessor architecture developed by Advanced Micro Devices that extended the 32-bit x86 instruction set to support 64-bit computing while preserving compatibility with existing 32-bit and 16-bit software. It enabled wider general-purpose registers, larger virtual and physical address spaces, and new calling conventions that influenced operating system and compiler designs. Its emergence reshaped server, desktop, and workstation markets and prompted competitive responses from Intel and software vendors.

History

AMD engineers designed the architecture in the late 1990s as a response to market needs identified by competitors such as Intel and research trends exemplified by projects at Stanford University and University of California, Berkeley. Initial public disclosure and implementation efforts involved collaboration with partners in the semiconductor ecosystem, including foundries like GlobalFoundries and design tool vendors such as Synopsys and Cadence Design Systems. The first commercial processors implementing the architecture launched in servers and workstations, entering markets dominated by processors from Intel Corporation and drawing attention from software maintainers at projects like Red Hat, Debian, and Canonical (company). Industry milestones included certification by enterprise vendors such as Oracle Corporation and adoption in supercomputing centers like Lawrence Livermore National Laboratory. Litigation and cross-licensing negotiations between AMD and Intel over x86 technologies influenced subsequent licensing of intellectual property and corporate strategy discussions involving firms like Advanced Micro Devices, Inc. and Via Technologies.

Architecture

The architecture extended the heritage of processors designed at companies such as Intel and innovations from academic teams at MIT and University of Illinois Urbana-Champaign by introducing 64-bit general-purpose registers, a unified flat memory model with 48-bit canonical addressing in many implementations, and revised privilege and segmentation semantics. Microarchitecture implementations implement pipelines, branch predictors, and out-of-order execution techniques developed in the lineage of designs by Arm Holdings and predecessors at Digital Equipment Corporation. The register file expansion influenced compilers maintained by projects like GCC and LLVM and calling conventions standardized in work by committees within IEEE and ISO. Memory management units and TLB designs echo research from Bell Labs and practical engineering choices seen in products by IBM and Sun Microsystems.

Instruction Set and Extensions

The instruction set preserved legacy opcodes used in software distributed by vendors such as Microsoft Corporation and Adobe Systems while adding 64-bit arithmetic, new addressing modes, and additional SSE and AVX vector extensions. Extensions were adopted over time, with implementations supporting vector and floating-point features developed in standards work by Intel and later broadened in ecosystem collaboration with researchers at Lawrence Berkeley National Laboratory. Compiler teams at Microsoft Visual Studio, GNU Project, and Clang integrated support for these extensions, enabling applications from scientific computing projects like NumPy and media frameworks maintained by FFmpeg to exploit SIMD improvements. Cryptography libraries such as those authored by contributors to OpenSSL and LibreSSL used new instructions for accelerated operations influenced by work at National Institute of Standards and Technology.

Operating System and Software Support

Broad support appeared across operating systems maintained by organizations including Microsoft Corporation, The FreeBSD Project, NetBSD Foundation, and the Linux Foundation. Major distributions from Red Hat, SUSE, and Canonical shipped kernels and userlands optimized for the architecture, while virtualization platforms from companies like VMware, Inc. and projects including KVM and Xen Project offered guests running 64-bit and 32-bit software. Development toolchains from GNU Project, LLVM Project, and Microsoft provided assemblers, linkers, and debuggers accounting for ABI changes. High-performance applications in databases from Oracle Corporation and analytics stacks like Hadoop and Spark (software) leveraged larger address spaces and memory models.

Performance and Implementation

Performance characteristics depended on microarchitectural choices by manufacturers including AMD and partners such as TSMC and GlobalFoundries. Later implementations adopted multi-core scaling, simultaneous multithreading, and sophisticated branch predictors inspired by research at Carnegie Mellon University and industrial designs from Intel. Benchmark suites maintained by organizations like SPEC and projects such as Phoronix Test Suite measured integer, floating-point, and memory throughput across releases. Power efficiency and thermal management drew on techniques used in products by NVIDIA and server designs from Dell Technologies and Hewlett Packard Enterprise. Real-world performance in scientific workloads referenced results from centers like Oak Ridge National Laboratory and industry reports by firms including Gartner.

Variants and Licensing

Variants of the architecture appeared in product families developed by firms such as AMD, and licensing discussions involved companies like Intel and VIA Technologies. Implementations varied across process nodes supplied by TSMC and GlobalFoundries, yielding parts marketed under series names by Advanced Micro Devices, Inc. and used in systems from Dell Technologies, HP, and Lenovo. Licensing models and cross-licensing settlements connected to cases adjudicated in courts involving United States District Court proceedings and influenced further collaboration between semiconductor firms and standards bodies like ISO and IEEE.

Category:Microprocessor architectures